Question: Preview File Edit View Go Tools Window Help v 4420spring 2015. 7. We assume a hypothetical CPU architecture which utilizes a paging-based memory management. The

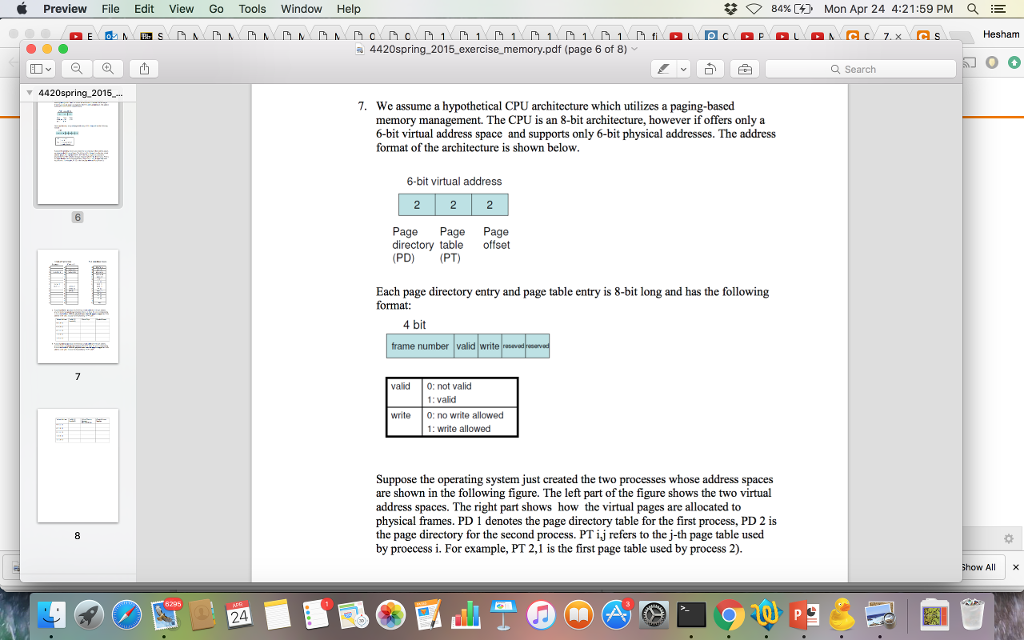

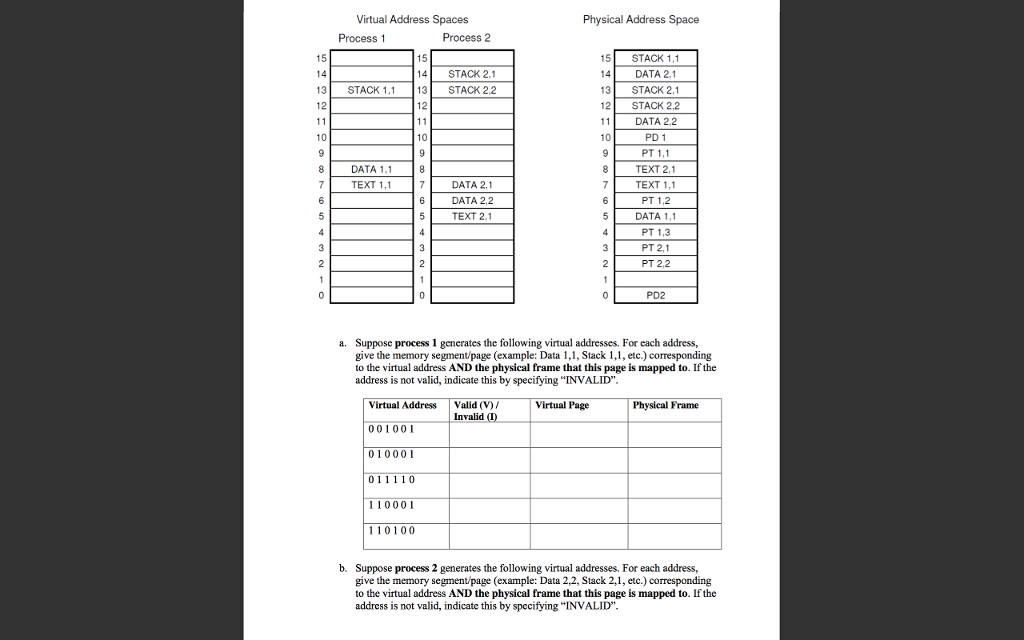

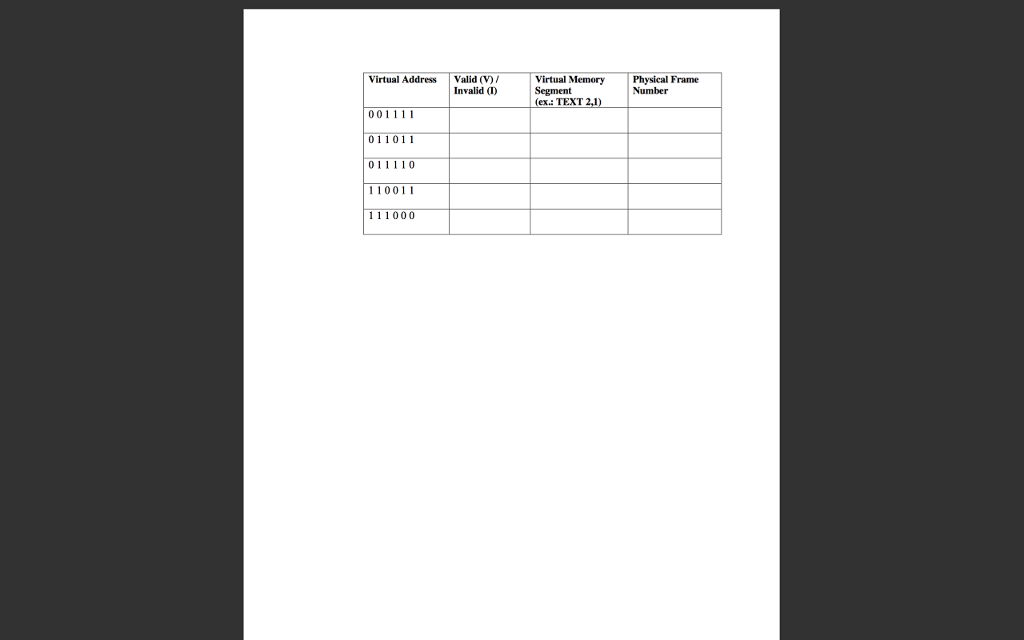

Preview File Edit View Go Tools Window Help v 4420spring 2015. 7. We assume a hypothetical CPU architecture which utilizes a paging-based memory management. The CPU is an 8-bit architecture, however ifoffers only a 6-bit virtual address space and supports only 6-bit physical addresses. The address format of the architecture is shown below. 6-bit virtual address 2 2 2 Page Page Page directory table offset (PD) PT Each page directory entry and page table entry is 8-bit long and has the following format 4 b frame number valid write rasevad valid 0: not valid write 0: no write allowed 1: write allowed Suppose the operating system just created the two processes whose address spaces are shown in the following figure. The left part of the figure shows the two virtual address spaces. The right part shows how the virtual pages are allocated to physical frames. PDI denotes the page directory table for the first process, PD 2 is the page directory for the second process. PTij refers to the j-th page table used by proecessi. For example, PT 2,1 is the first page table used by process 20. Mon Apr 24 4:21:59 PM a Hesham Search Preview File Edit View Go Tools Window Help v 4420spring 2015. 7. We assume a hypothetical CPU architecture which utilizes a paging-based memory management. The CPU is an 8-bit architecture, however ifoffers only a 6-bit virtual address space and supports only 6-bit physical addresses. The address format of the architecture is shown below. 6-bit virtual address 2 2 2 Page Page Page directory table offset (PD) PT Each page directory entry and page table entry is 8-bit long and has the following format 4 b frame number valid write rasevad valid 0: not valid write 0: no write allowed 1: write allowed Suppose the operating system just created the two processes whose address spaces are shown in the following figure. The left part of the figure shows the two virtual address spaces. The right part shows how the virtual pages are allocated to physical frames. PDI denotes the page directory table for the first process, PD 2 is the page directory for the second process. PTij refers to the j-th page table used by proecessi. For example, PT 2,1 is the first page table used by process 20. Mon Apr 24 4:21:59 PM a Hesham Search

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts