Question: Problem 0 2 : ( 3 5 points ) This exercise is intended to help you understand the cost / complexity / performance trade -

Problem : points This exercise is intended to help you understand the costcomplexityperformance tradeoffs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined datapaths from Figure textbook

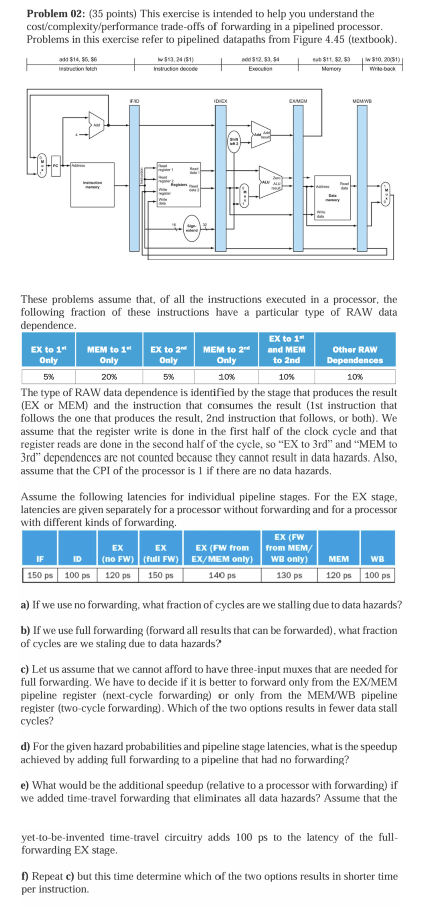

These problems assume that, of all the instructions executed in a processor, the following fraction of these instructions have a particular type of RAW data dependence.

The type of RAW data dependence is identified by the stage that produces the result EX or MEM and the instruction that consumes the result st instruction that follows the one that produces the result, nd instruction that follows, or both We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle, so EX to rd and "MEM to rd dependences are not counted because they cannot result in data hazards. Also, assume that the CPI of the processor is if there are no data hazards.

Assume the following latencies for individual pipeline stages. For the EX stage, latencies are given separately for a processor without forwarding and for a processor with different kinds of forwarding.

a If we use no forwarding, what fraction of cycles are we stalling due to data hazards?

b If we use full forwarding forward all results that can be forwarded what fraction of cycles are we staling due to data hazards?

c Let us assume that we cannot afford to have threeinput muxes that are needed for full forwarding. We have to decide if it is better to forward only from the EXMEM pipeline register nextcycle forwarding or only from the MEMWB pipeline register twocycle forwarding Which of the two options results in fewer data stall cycles?

d For the given hazard probabilities and pipeline stage latencies, what is the speedup achieved by adding full forwarding to a pipeline that had no forwarding?

e What would be the additional speedup relative to a processor with forwarding if we added timetravel forwarding that eliminates all data hazards? Assume that the

yettobeinvented timetravel circuitry adds ps to the latency of the fullforwarding EX stage.

f Repeat c but this time determine which of the two options results in shorter time per instruction.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock