Question: Problem 1 ( 6 0 points ) . Consider the complete MIPS pipelined datapath that we have learned, which is capable of detecting hazards, using

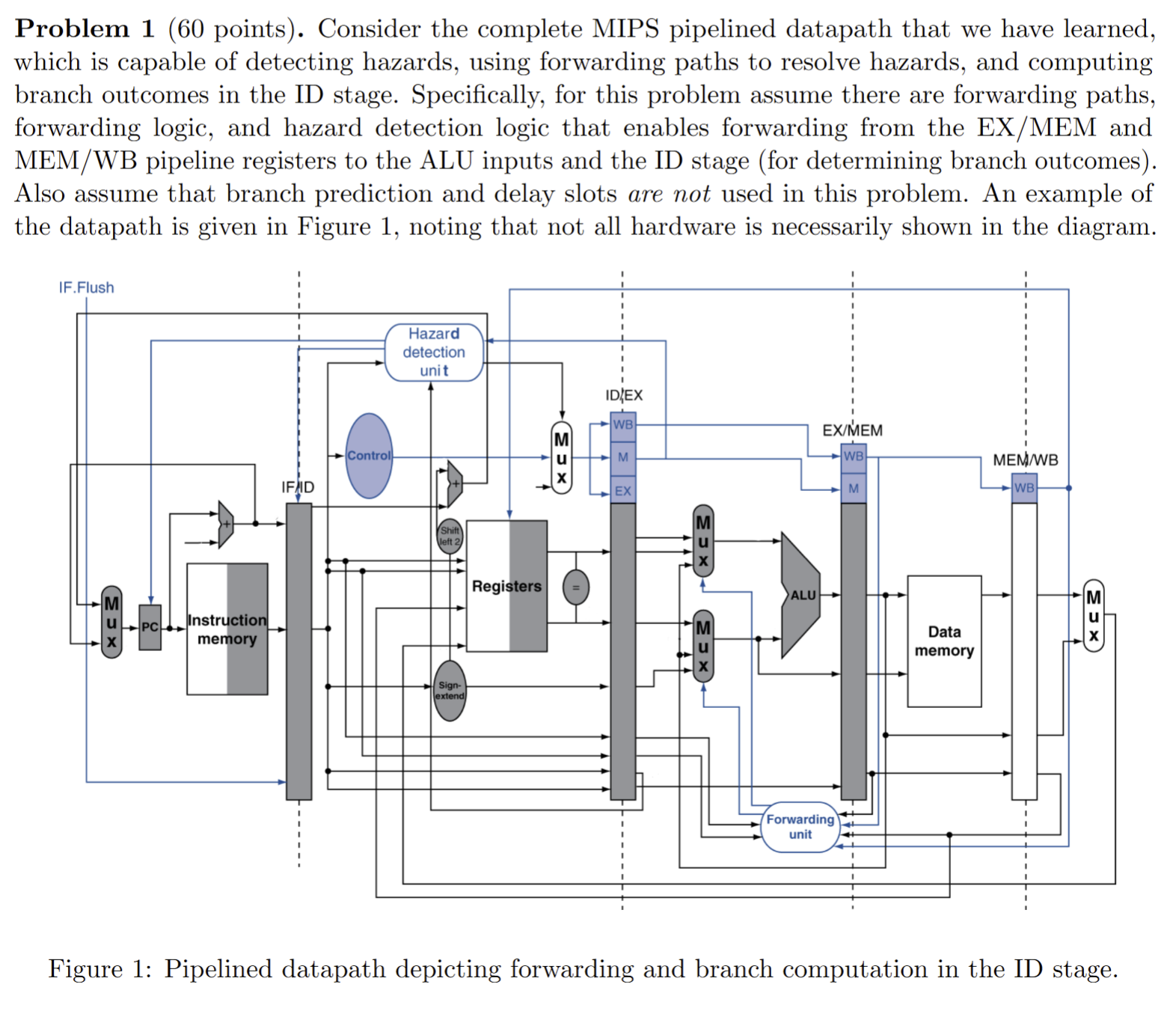

Problem points Consider the complete MIPS pipelined datapath that we have learned, which is capable of detecting hazards, using forwarding paths to resolve hazards, and computing branch outcomes in the ID stage. Specifically, for this problem assume there are forwarding paths, forwarding logic, and hazard detection logic that enables forwarding from the EXMEM and MEMWB pipeline registers to the ALU inputs and the ID stage for determining branch outcomes Also assume that branch prediction and delay slots are not used in this problem. An example of the datapath is given in Figure noting that not all hardware is necessarily shown in the diagram. Figure : Sample pipeline execution diagram. Draw the pipeline execution diagram for the two sequences of instructions given below when

executed in the pipelined datapath described above. For sequence A assume the branch instruction is not taken, and for sequence B assume the branch instruction is taken. Your pipeline execution diagram should clearly indicate the forwarding paths that may be used and clearly mark a bubble ie stalled instruction An example of a pipeline execution diagram is given in Figure You must draw a similar diagram but for the following sequences of instructions:

Sequence A

add $t $t $t

ori $t $txF

lw tt

beq $t $t LABEL

sw tt

Sequence B

sub $t $t $t

and $t $t $t

add $t $t $t

beq $t $t LABEL

lw tt

LABEL: w tt Problem points Consider the complete MIPS pipelined datapath that we have learned, which is capable of detecting hazards, using forwarding paths to resolve hazards, and computing branch outcomes in the ID stage. Specifically, for this problem assume there are forwarding paths, forwarding logic, and hazard detection logic that enables forwarding from the EXMEM and MEMWB pipeline registers to the ALU inputs and the ID stage for determining branch outcomes Also assume that branch prediction and delay slots are not used in this problem. An example of the datapath is given in Figure noting that not all hardware is necessarily shown in the diagram.

Figure : Pipelined datapath depicting forwarding and branch computation in the ID stage.

Figure : Sample pipeline execution diagram.

Draw the pipeline execution diagram for the two sequences of instructions given below when executed in the pipelined datapath described above. For sequence A assume the branch instruction is not taken, and for sequence B assume the branch instruction is taken. Your pipeline execution diagram should clearly indicate the forwarding paths that may be used and clearly mark a bubble ie stalled instruction An example of a pipeline execution diagram is given in Figure You must draw a similar diagram but for the following sequences of instructions:

Sequence A

add $t $t $t

ori $t $txF

lw $t$t

beq $t $t LABEL

sw $t$t

Sequence B

sub $t$t$t

and $t$t$t

add $t$t$t

beq $t$t LABEL

w $t$t

LABEL: w $t$t

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock