Question: Problem 2: ( 8 pts) Part 1: (4 pts) Translate the below C code into RISC-V architecture, assuming that the values of j and k

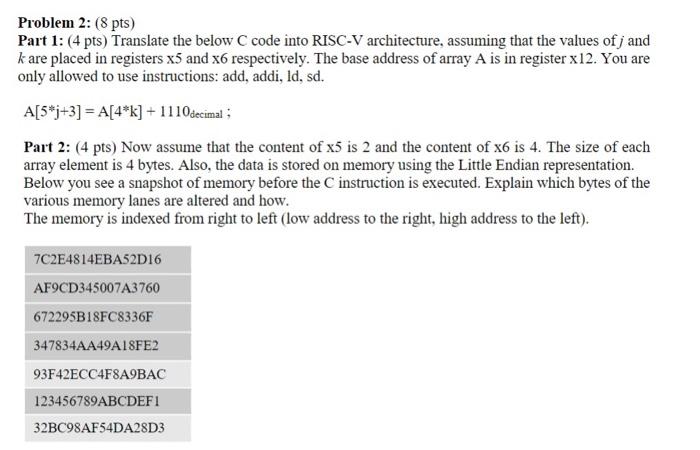

Problem 2: ( 8 pts) Part 1: (4 pts) Translate the below C code into RISC-V architecture, assuming that the values of j and k are placed in registers x5 and x6 respectively. The base address of array A is in register x12. You are only allowed to use instructions: add, addi, ld, sd. A[5j+3]=A[4k]+1110decimal Part 2: (4 pts) Now assume that the content of x5 is 2 and the content of x6 is 4 . The size of each array element is 4 bytes. Also, the data is stored on memory using the Little Endian representation. Below you see a snapshot of memory before the C instruction is executed. Explain which bytes of the various memory lanes are altered and how. The memory is indexed from right to left (low address to the right, high address to the left)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts