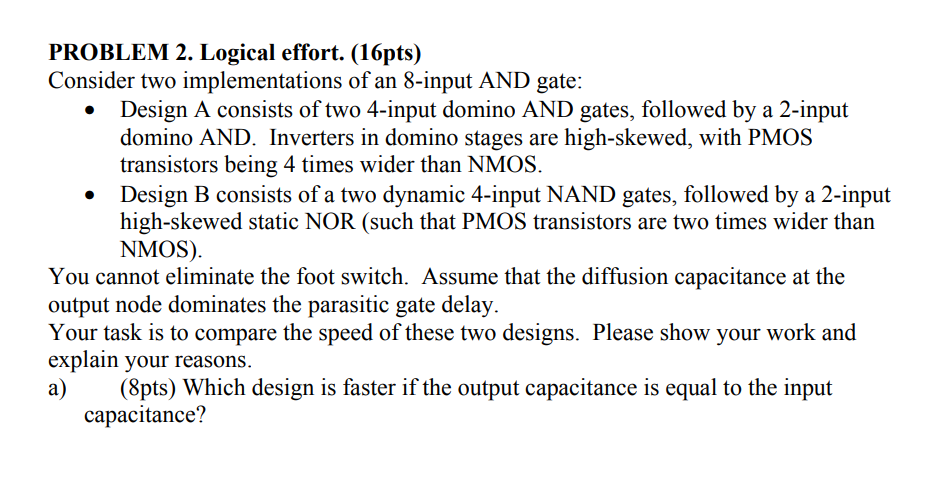

Question: PROBLEM 2 . Logical effort. ( 1 6 pts ) Consider two implementations of an 8 - input AND gate: - Design A consists of

PROBLEM Logical effort. pts

Consider two implementations of an input AND gate:

Design A consists of two input domino AND gates, followed by a input domino AND. Inverters in domino stages are highskewed, with PMOS transistors being times wider than NMOS.

Design B consists of a two dynamic input NAND gates, followed by a input highskewed static NOR such that PMOS transistors are two times wider than NMOS

You cannot eliminate the foot switch. Assume that the diffusion capacitance at the output node dominates the parasitic gate delay.

Your task is to compare the speed of these two designs. Please show your work and explain your reasons.

apts Which design is faster if the output capacitance is equal to the input capacitance?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock