Question: Problem # 2 : Suppose processors P 1 and P 2 have private and snoopy caches. Both caches are initially empty. Consider the sequence of

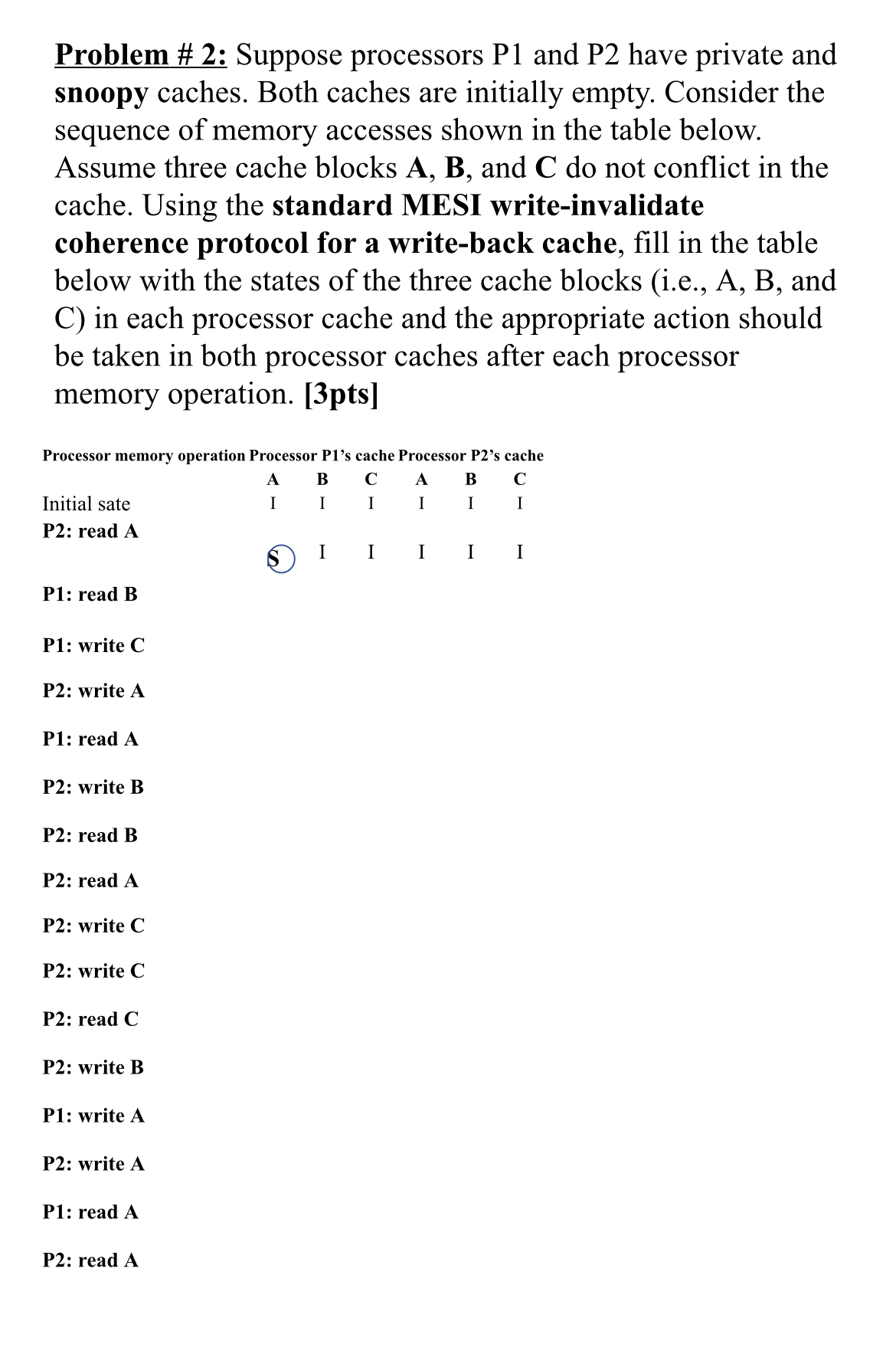

Problem # : Suppose processors P and P have private and snoopy caches. Both caches are initially empty. Consider the sequence of memory accesses shown in the table below. Assume three cache blocks and do not conflict in the cache. Using the standard MESI writeinvalidate coherence protocol for a writeback cache, fill in the table below with the states of the three cache blocks ie A B and C in each processor cache and the appropriate action should be taken in both processor caches after each processor memory operation. pts

Processor memory operation Processor Ps cache Processor Ps cache

Initial sate

P: readA

P: read

P: write

P: write A

:readA

P: write B

P: read B

P: readA

P: write

P: write C

P: read

P: write B

P: write A

P: write A

:readA

:readA

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock