Question: Problem 3 15 points Suppose we have a single-cycle datapath implementation (refer to the previous figure) with the following properties Reading or writing to instruction

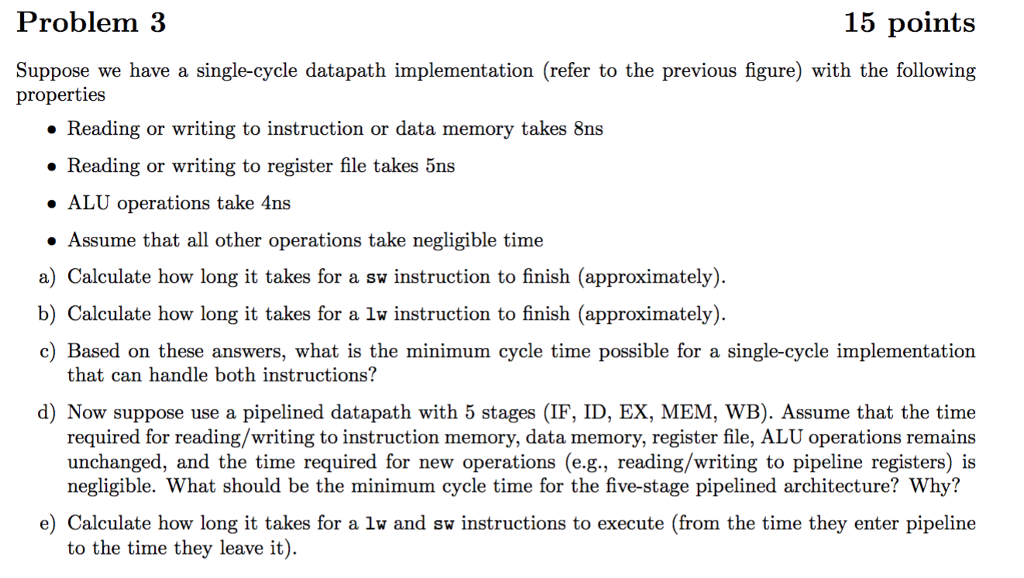

Problem 3 15 points Suppose we have a single-cycle datapath implementation (refer to the previous figure) with the following properties Reading or writing to instruction or data memory takes 8ns Reading or writing to register file takes 5ns ALU operations take 4ns Assume that all other operations take negligible time a) Calculate how long it takes for a sw instruction to finish (approximately). b) Calculate how long it takes for a lw instruction to finish (approximately). c) Based on these answers, what is the minimum cycle time possible for a single-cycle implementation that can handle both instructions? d) Now suppose use a pipelined datapath with 5 stages (IF, ID, EX, MEM, WB). Assume that the time required for reading/writing to instruction memory, data memory, register file, ALU operations remains unchanged, and the time required for new operations (e.g., reading writing to pipeline registers) is negligible. What should be the minimum cycle time for the five-stage pipelined architecture? Why? e) Calculate how long it takes for a lw and sw instructions to execute (from the time they enter pipeline to the time they leave it)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts