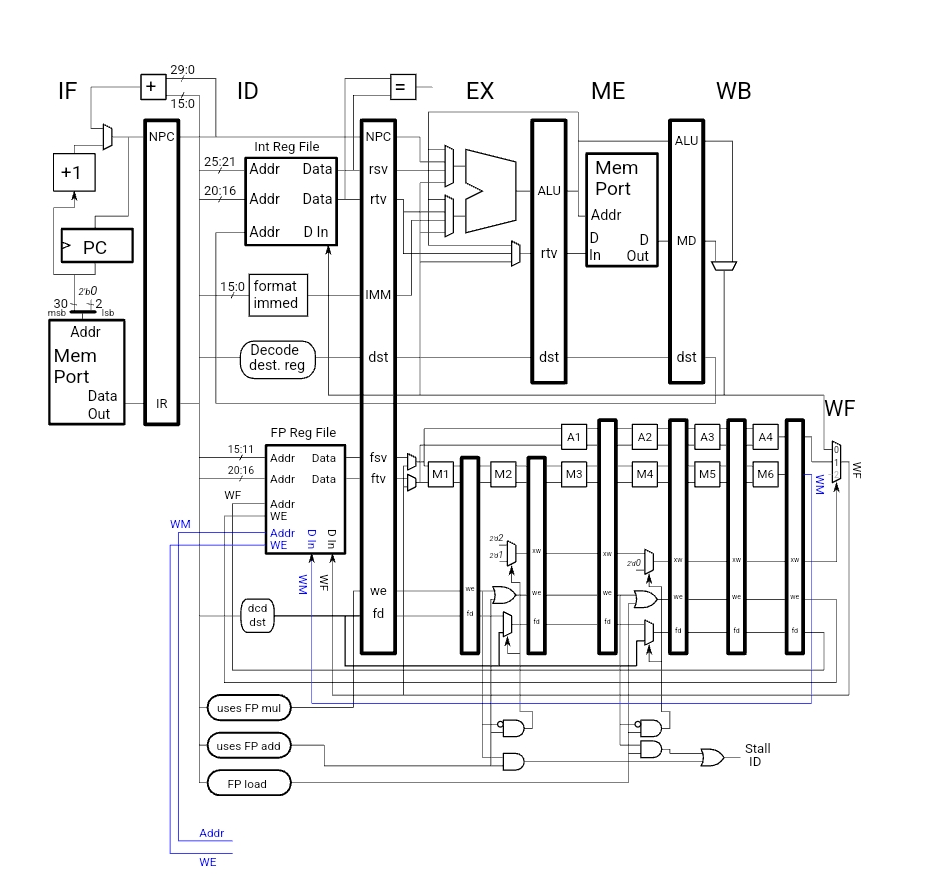

Question: Problem 3 : ( 2 0 p t s ) In the incomplete MIPS implementation to the right the FP multiply unit has its own

Problem : In the incomplete MIPS implementation to the right the FP multiply unit has its own write port to the FP register file, shown in blue and labeled WM in several places. Because of this new MW port the sub.s instruction in the execution below does not stall, both the sub.s and mul.s can write back in cycle The control logic has not yet been updated for MWa With the illustrated hardware a result cannot be bypassed from a mul.s to another instruction. The last add.s suffers a stall because of that. Add bypass hardware for such cases.

Add the bypass hardware.

Try to keep cost down by using one mux.

b Modify the control logic so that it no longer stalls instructions that would write back through WF at the same time as a preceding mul.s Hint: This is just a matter of crossing things out.

Modify logic to eliminate stalls due to mul.s but retain stalls for instructions contending for WF such as lwc in execution above.

c Provide the correct Addr and WE signals to the WM and WF ports of the FP register file. Note that the WF ports are connected, but based on the original version. The WM port wires are shown unconnected on the lowerleft of the diagram.

Add hardware for the MW Addr and WE signals, and make changes to the WF Addr and WE signals.

Cross out unneeded hardware and simplify remaining hardware where possible.

ID formatlimmeddest regFP Reg FilWMWEOuses FP addFP loadDEXHDMEWEWMNE

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock