Question: Problems: 1. How long will the following code fragment take to issue on an in-order superscalar processor with three execution units, where all instructions have

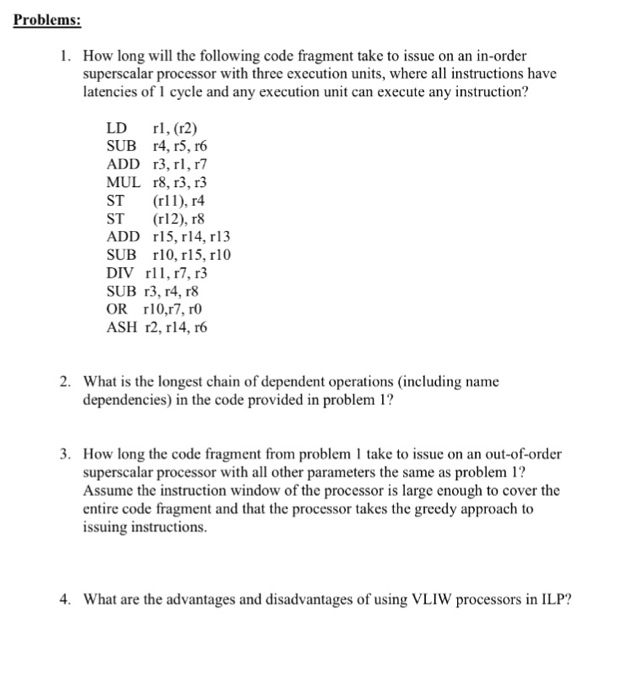

Problems: 1. How long will the following code fragment take to issue on an in-order superscalar processor with three execution units, where all instructions have latencies of 1 cycle and any execution unit can execute any instruction? LD r, (r2) SUB r4, r5, r6 ADD r3, r, r7 MUL r8, r3, r3 ST (r1), r4 ST (r12), r8 ADD rl5, r14, r13 SUB r10, rl5, r10 DIV r, r7, r3 SUB r3, r4, r8 OR r10,r7, r0 2. What is the longest chain of dependent operations (including name dependencies) in the code provided in problem 1? 3. How long the code fragment from problem 1 take to issue on an out-of-order superscalar processor with all other parameters the same as problem 1? Assume the instruction window of the processor is large enough to cover the entire code fragment and that the processor takes the greedy approach to issuing instructions. 4. What are the advantages and disadvantages of using VLIW processors in ILP

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts