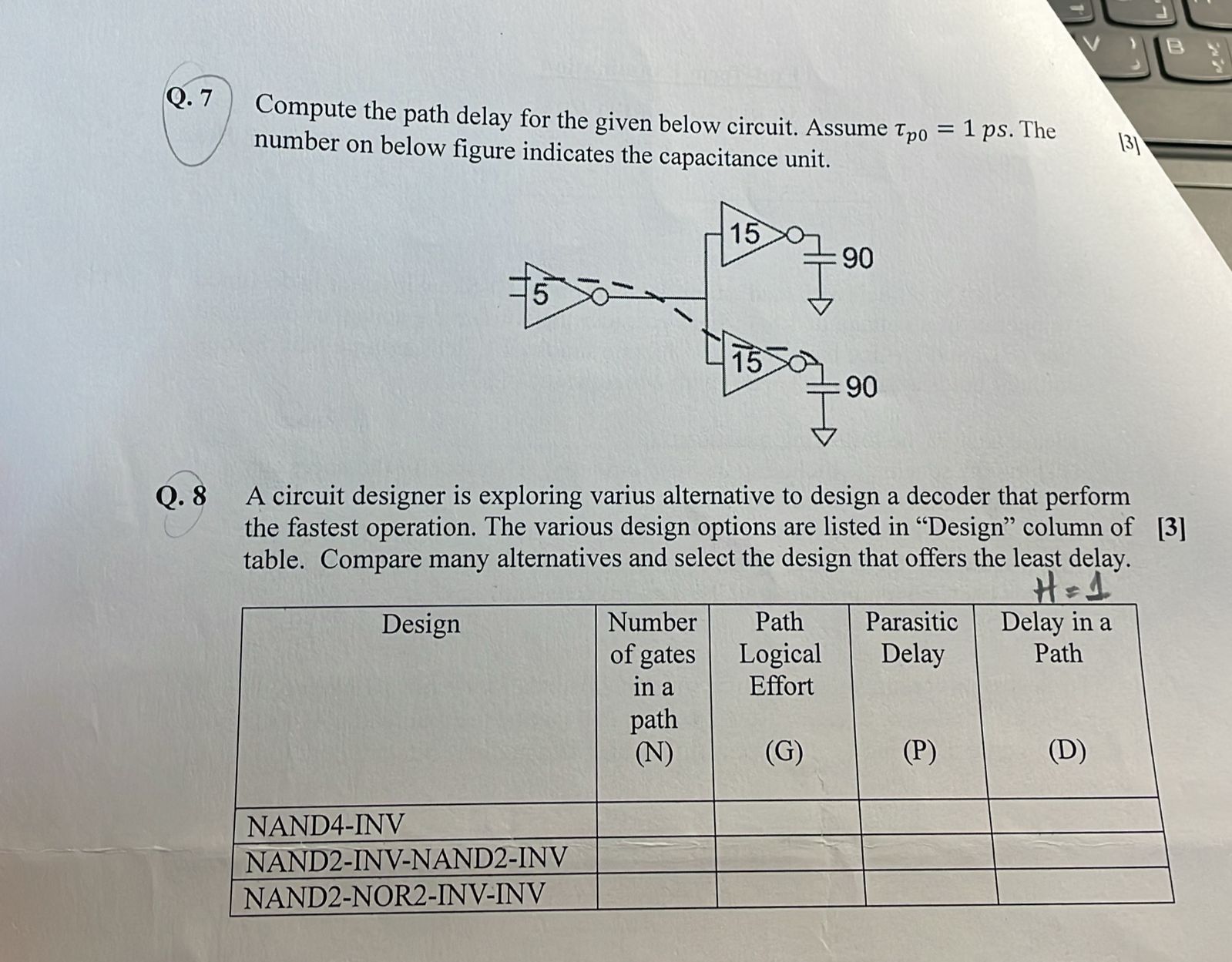

Question: Q . 7 Compute the path delay for the given below circuit. Assume ( tau _ { p 0 } = 1

Q Compute the path delay for the given below circuit. Assume taup mathrmps The number on below figure indicates the capacitance unit.

Q A circuit designer is exploring varius alternative to design a decoder that perform the fastest operation. The various design options are listed in "Design" column of

table. Compare many alternatives and select the design that offers the least delay.

begintabularlcccc

hline multicolumnc Design & begintabularc

Number

of gates

in a

path

N

endtabular & begintabularc

Path

Logical

Effort

endtabular & begintabularc

Parasitic

Delay

endtabular & begintabularc

Delay in a

Path

endtabular

hline NANDINV & & & P & D

hline NANDINVNANDINV & & & &

hline NANDNORINVINV & & & &

hline

endtabular

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock