Question: Q1 (a) List five cycles in instruction execution. (5 marks) (b) Explain the pipeline evolution. (4 marks) Write a program using any Instruction Set Architecture

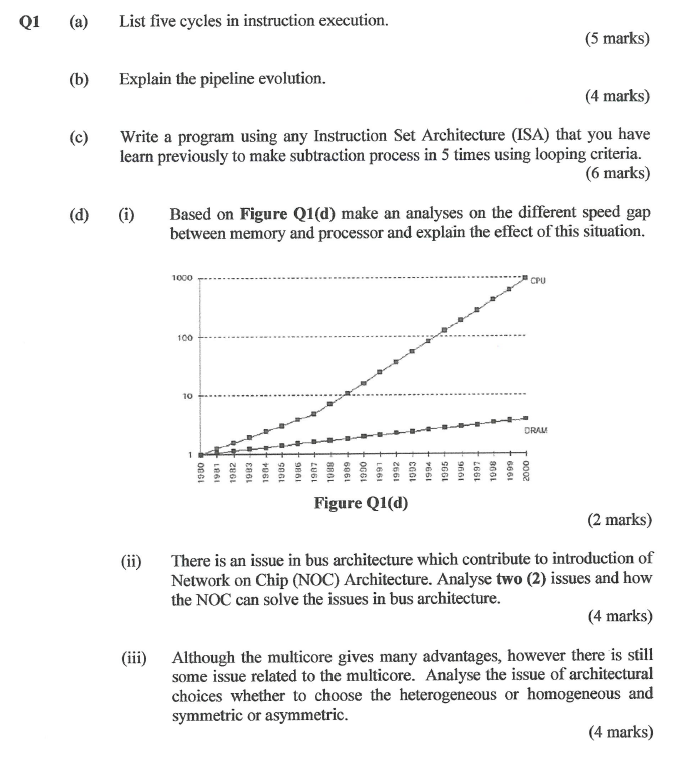

Q1 (a) List five cycles in instruction execution. (5 marks) (b) Explain the pipeline evolution. (4 marks) Write a program using any Instruction Set Architecture (ISA) that you have learn previously to make subtraction process in 5 times using looping criteria. (6 marks) (i) Based on Figure Q1(d) make an analyses on the different speed gap between memory and processor and explain the effect of this situation. (d) 1000 CPU 100 10 DRAU 1 1900 of 286 981 Enou 1961 1005 1088 1909 1992 1993 7661 SGGI 1996 1997 1008 6661 2000 Figure Q1(d) (2 marks) (ii) There is an issue in bus architecture which contribute to introduction of Network on Chip (NOC) Architecture. Analyse two (2) issues and how the NOC can solve the issues in bus architecture. (4 marks) (iii) Although the multicore gives many advantages, however there is still some issue related to the multicore. Analyse the issue of architectural choices whether to choose the heterogeneous or homogeneous and symmetric or asymmetric. (4 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts