Question: Q1. Cache (a) Assume that addresses are 32 bits long, that the 5 low order bits of an address are used for the offset into

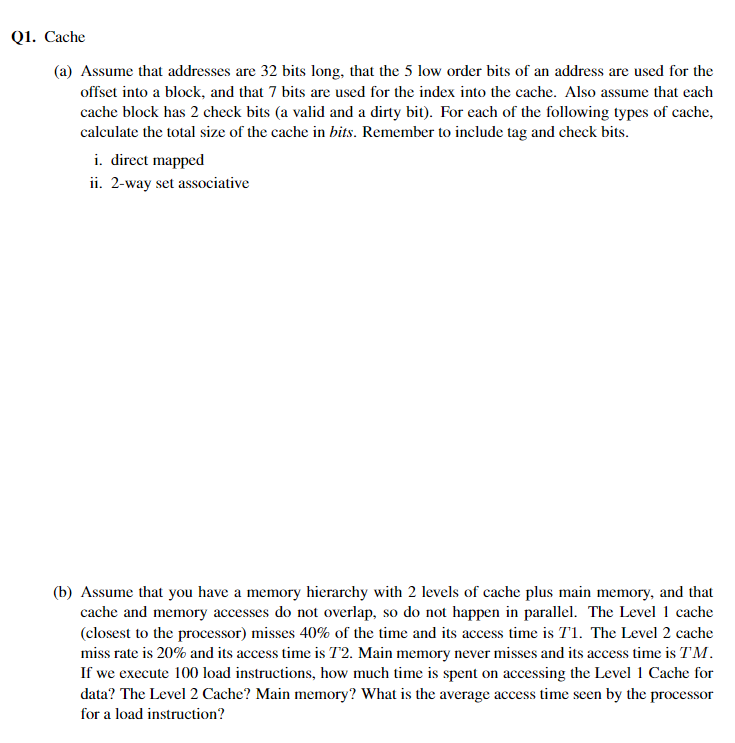

Q1. Cache (a) Assume that addresses are 32 bits long, that the 5 low order bits of an address are used for the offset into a block, and that 7 bits are used for the index into the cache. Also assume that each cache block has 2 check bits (a valid and a dirty bit). For each of the following types of cache, calculate the total size of the cache in bits. Remember to include tag and check bits i. direct mapped ii. 2-way set associative (b) Assume that you have a memory hierarchy with 2 levels of cache plus main memory, and that cache and memory accesses do not overlap, so do not happen in parallel. The Level 1 cache (closest to the processor) misses 40% of the time and its access time is TI, The Level 2 cache miss rate is 20% and its access time is T2. Main memory never misses and its access time is TM. If we execute 100 load instructions, how much time is spent on accessing the Level 1 Cache for data? The Level 2 Cache? Main memory? What is the average access time seen by the processor for a load instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts