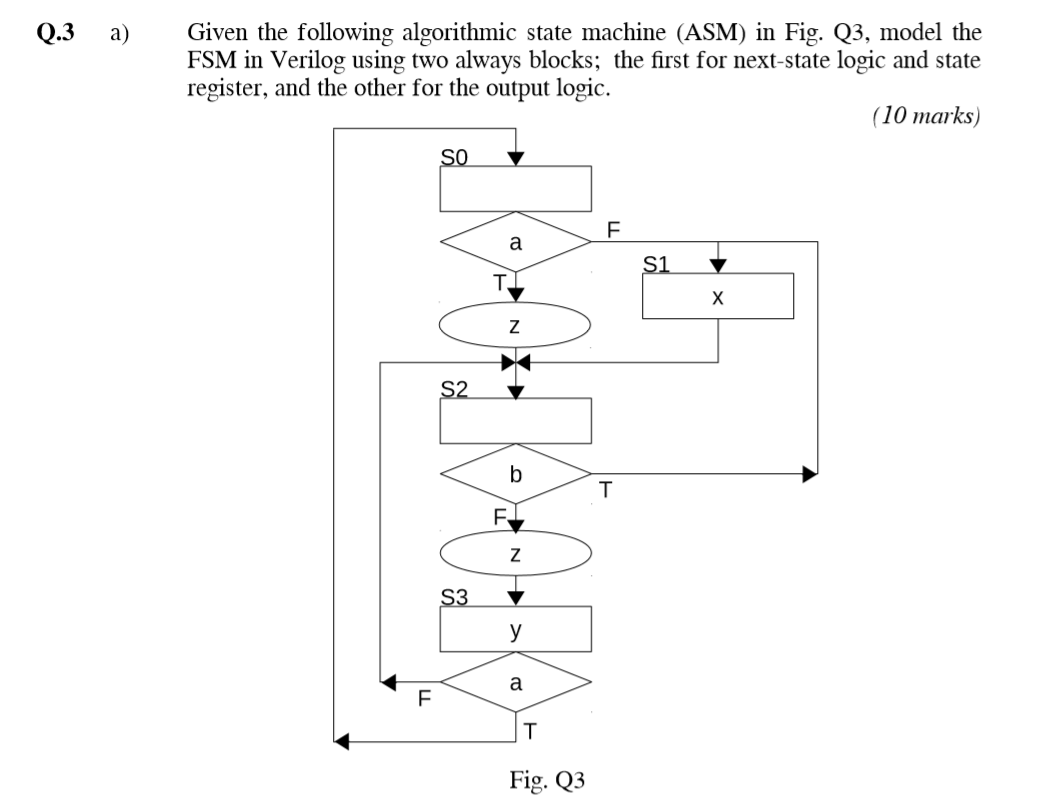

Question: Q.3 a) Given the following algorithmic state machine (ASM) in Fig. Q3, model the FSM in Verilog using two always blocks; the first for next-state

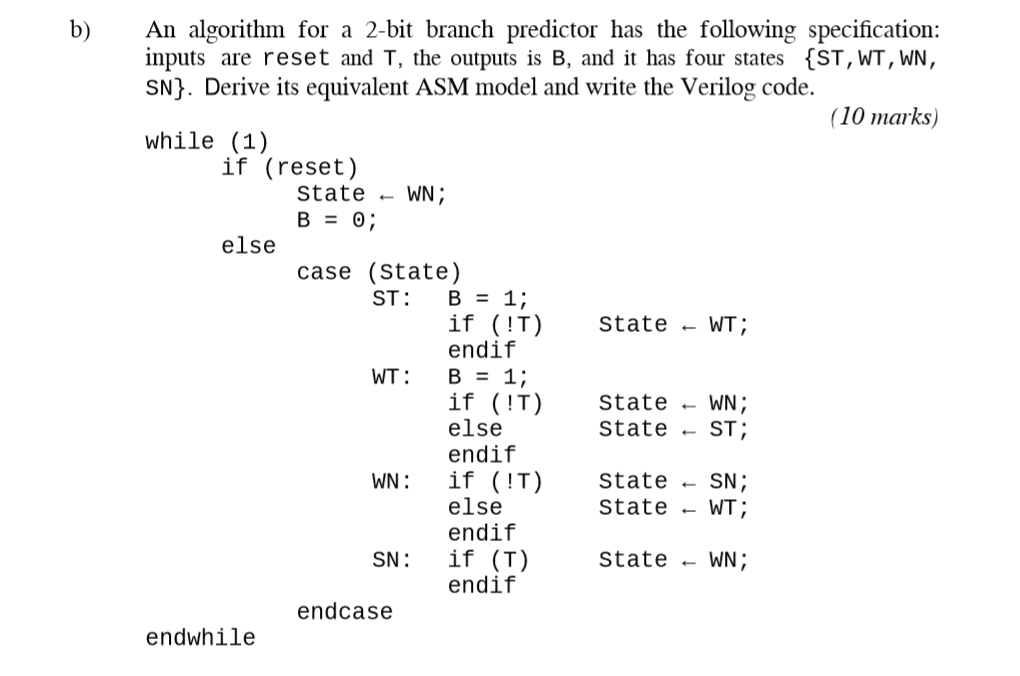

Q.3 a) Given the following algorithmic state machine (ASM) in Fig. Q3, model the FSM in Verilog using two always blocks; the first for next-state logic and state register, and the other for the output logic. (10 marks) SO F a S1 T X Z FO: FF S2 b T F Z S3 E T Fig. 23 b) An algorithm for a 2-bit branch predictor has the following specification: inputs are reset and T, the outputs is B, and it has four states {ST, WT, WN, SN}. Derive its equivalent ASM model and write the Verilog code. (10 marks) while (1) if (reset) state - WN; B = 0; else case (state) ST: B = 1; if (!T) State WT; endir WT: B = 1; if (!T) state WN; else state - ST; endif WN : if (!T) state SN; else state endif SN: if (T) State WN; endir endcase endwhile - WT; Q.3 a) Given the following algorithmic state machine (ASM) in Fig. Q3, model the FSM in Verilog using two always blocks; the first for next-state logic and state register, and the other for the output logic. (10 marks) SO F a S1 T X Z FO: FF S2 b T F Z S3 E T Fig. 23 b) An algorithm for a 2-bit branch predictor has the following specification: inputs are reset and T, the outputs is B, and it has four states {ST, WT, WN, SN}. Derive its equivalent ASM model and write the Verilog code. (10 marks) while (1) if (reset) state - WN; B = 0; else case (state) ST: B = 1; if (!T) State WT; endir WT: B = 1; if (!T) state WN; else state - ST; endif WN : if (!T) state SN; else state endif SN: if (T) State WN; endir endcase endwhile - WT

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts