Question: Question 0 3 : Investigate and compare the memory efficiency of five distinct instruction set architectures when executing the provided code sequence. Each architecture has

Question :

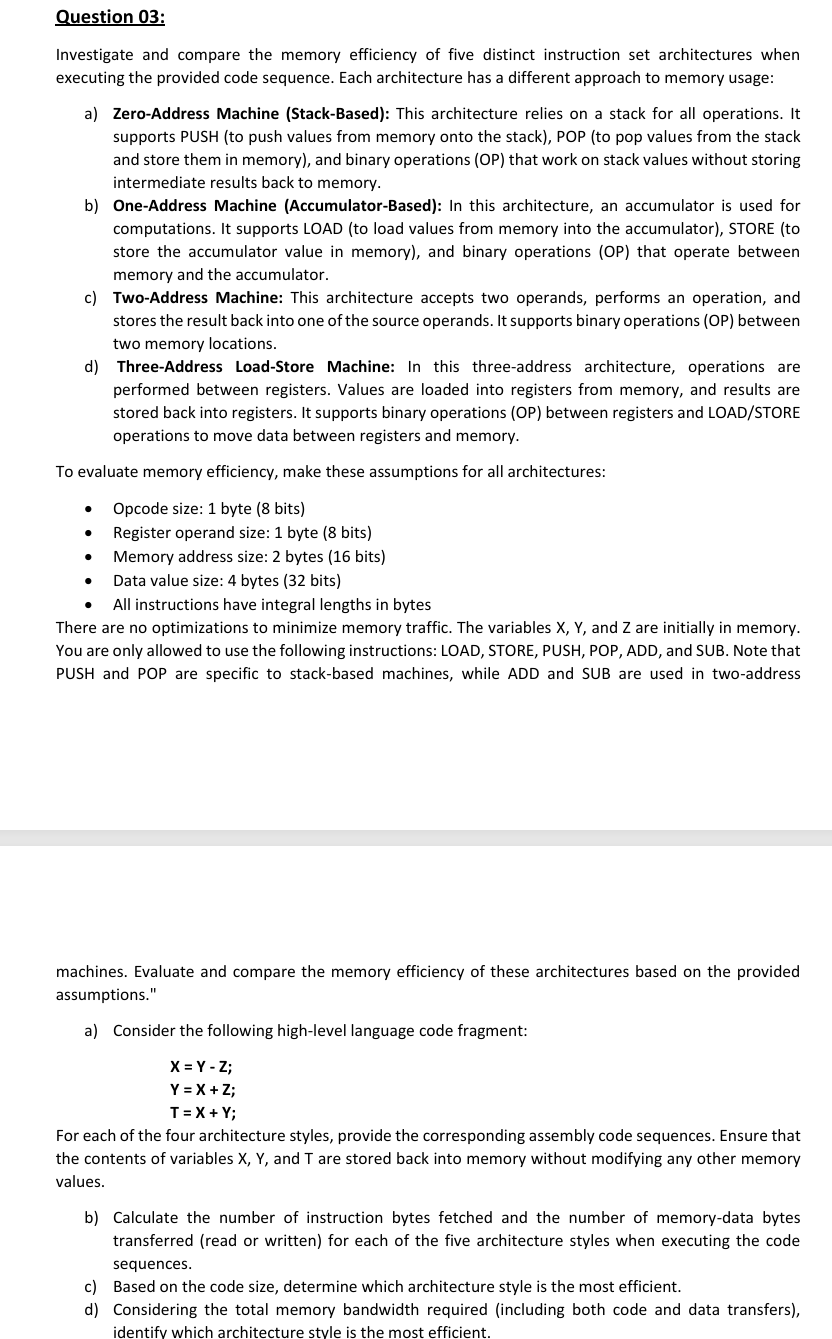

Investigate and compare the memory efficiency of five distinct instruction set architectures when

executing the provided code sequence. Each architecture has a different approach to memory usage:

a ZeroAddress Machine StackBased: This architecture relies on a stack for all operations. It

supports PUSH to push values from memory onto the stack POP to pop values from the stack

and store them in memory and binary operations OP that work on stack values without storing

intermediate results back to memory.

b OneAddress Machine AccumulatorBased: In this architecture, an accumulator is used for

computations. It supports LOAD to load values from memory into the accumulator STORE to

store the accumulator value in memory and binary operations OP that operate between

memory and the accumulator.

c TwoAddress Machine: This architecture accepts two operands, performs an operation, and

stores the result back into one of the source operands. It supports binary operations OP between

two memory locations.

d ThreeAddress LoadStore Machine: In this threeaddress architecture, operations are

performed between registers. Values are loaded into registers from memory, and results are

stored back into registers. It supports binary operations OP between registers and LOADSTORE

operations to move data between registers and memory.

To evaluate memory efficiency, make these assumptions for all architectures:

Opcode size: byte bits

Register operand size: byte bits

Memory address size: bytes bits

Data value size: bytes bits

All instructions have integral lengths in bytes

There are no optimizations to minimize memory traffic. The variables and Z are initially in memory.

You are only allowed to use the following instructions: LOAD, STORE, PUSH, POP, ADD, and SUB. Note that

PUSH and POP are specific to stackbased machines, while ADD and SUB are used in twoaddress

machines. Evaluate and compare the memory efficiency of these architectures based on the provided

assumptions."

a Consider the following highlevel language code fragment:

For each of the four architecture styles, provide the corresponding assembly code sequences. Ensure that

the contents of variables and T are stored back into memory without modifying any other memory

values.

b Calculate the number of instruction bytes fetched and the number of memorydata bytes

transferred read or written for each of the five architecture styles when executing the code

sequences.

c Based on the code size, determine which architecture style is the most efficient.

d Considering the total memory bandwidth required including both code and data transfers

identify which architecture style is the most efficient.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock