Question: Question 1 (a) Briefly describe the 4 main structural components of a processor. (8 marks) (b) Explain Moore's law. (3 marks) (c) Consider two hypothetical

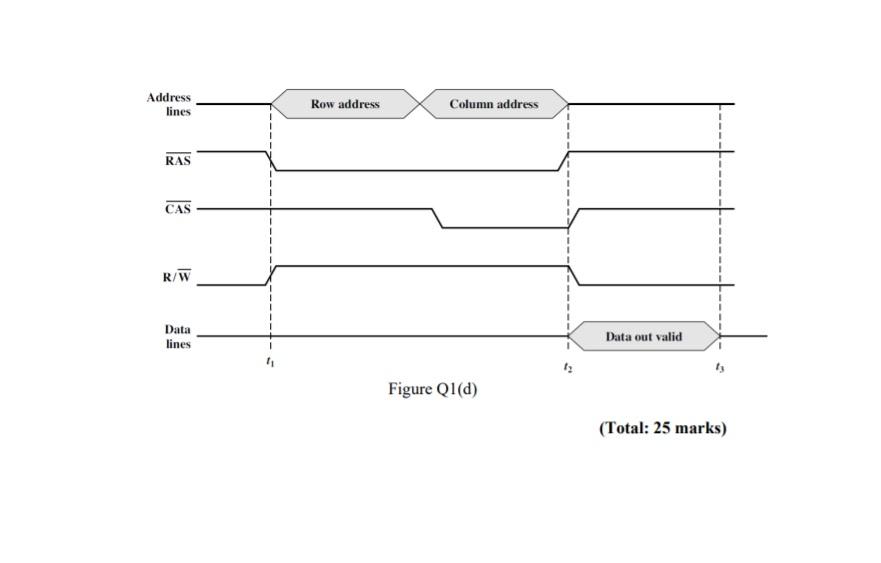

Question 1 (a) Briefly describe the 4 main structural components of a processor. (8 marks) (b) Explain Moore's law. (3 marks) (c) Consider two hypothetical microprocessor that use 16-bit addresses (ie, the program counter and the address registers are 16-bit wide) and 16-bit data buses. (i) Solve (calculate) for the maximum memory address space and data transfer speed of the two processors if they are respectively connected to "32-bit memory" and "16-bit memory. (4 marks) (d) If the processors use an input and an output instruction that can specify X-bit I/O port numbers, solve for the number of 16-bit 1/0 ports each of the microprocessors can support. (3 marks) The timing diagram for a DRAM read operation over a bus is shown in Figure Q1(d). The bus cycle is considered to last from 11 to 12, after which there is a recharge time lasting from 12 to t3. The recharge time is required for the DRAM chip's refresh operations and must be completed before the microprocessor can access the chip again. (i) Assuming that the access time is 6Xns and the recharge time is 4Xns, solve for the maximum data rate this DRAM chip can sustain assuming a l-bit output. (4 marks) (ii) If a IX-bit wide memory system is implemented using these DRAM chips, analyze the performance of the system in terms of data transfer rate in MB/s. memory (3 marks) Address lines Row address Column address RAS CAS R/W Data lines Data out valid Figure Q1(d) (Total: 25 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts