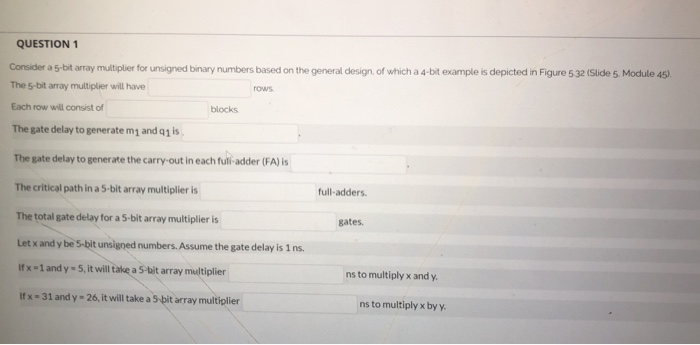

Question: QUESTION 1 Consider a 5-bit array multiplier for unsigned binary numbers based on the general design of which a 4-bit example is depicted in Figure

QUESTION 1 Consider a 5-bit array multiplier for unsigned binary numbers based on the general design of which a 4-bit example is depicted in Figure 532 (Slide 5. Module 45) The 5-bit array multiplier will have Each row will consist of The gate delay to generate m1 and q1is The gate delay to generate the carry-out in each fuli-adder (FA) is The critical path in a 5-bit array multiplier is The total gate delay for a 5-bit array multiplier is Let x and y be S-bit unsigned numbers. Assume the gate delay is 1 ns. rows blocks full-adders. gates. x-1 and y 5, it will take a 5-bit array meltiplier ns to multiply x and y #x-31 and y-26, it will take a stt array multiplier ns to multiply x by y QUESTION 1 Consider a 5-bit array multiplier for unsigned binary numbers based on the general design of which a 4-bit example is depicted in Figure 532 (Slide 5. Module 45) The 5-bit array multiplier will have Each row will consist of The gate delay to generate m1 and q1is The gate delay to generate the carry-out in each fuli-adder (FA) is The critical path in a 5-bit array multiplier is The total gate delay for a 5-bit array multiplier is Let x and y be S-bit unsigned numbers. Assume the gate delay is 1 ns. rows blocks full-adders. gates. x-1 and y 5, it will take a 5-bit array meltiplier ns to multiply x and y #x-31 and y-26, it will take a stt array multiplier ns to multiply x by y

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts