Question: Question 2: (Interrupts) Write the C code to define an ISR that handles UART1 peripheral interrupt on the Teensy 3.2. If you enable an interrupt

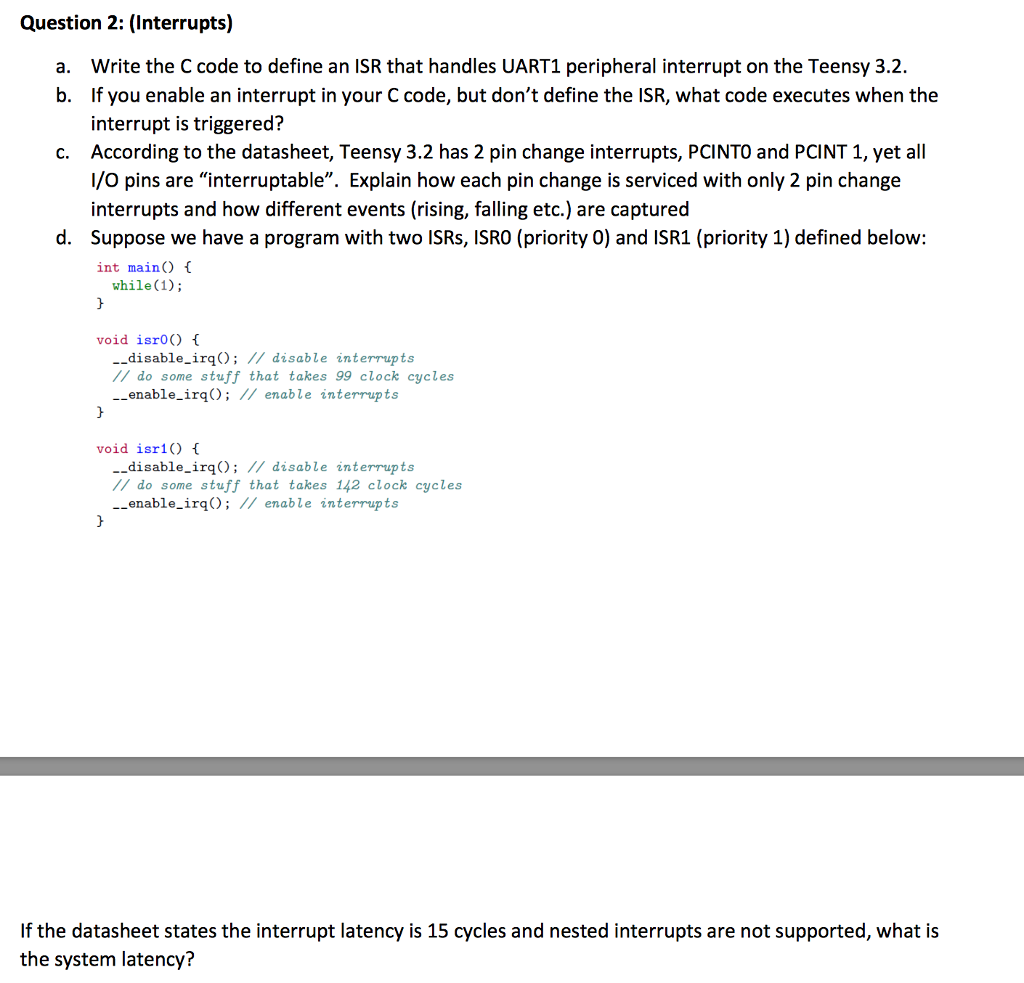

Question 2: (Interrupts) Write the C code to define an ISR that handles UART1 peripheral interrupt on the Teensy 3.2. If you enable an interrupt in your C code, but don't define the ISR, what code executes when the interrupt is triggered? According to the datasheet, Teensy 3.2 has 2 pin change interrupts, PCINTO and PCINT1, yet all I/O pins are "interruptable". Explain how each pin change is serviced with only 2 pin change interrupts and how different events (rising, falling etc.) are captured Suppose we have a program with two ISRs, ISRO (priority 0) and ISR1 (priority 1) defined below: int mainO a. b. c. d. while(1) void isro0 _.disable_irq); I/disable interrupts do some stuff that takes 99 clock cycles .enableirq); I/ enable interrupts void isr10 _disable_irq) / disable interrupts do some stuff that takes 142 clock cycles .enable.irq); // enable interrupts If the datasheet states the interrupt latency is 15 cycles and nested interrupts are not supported, what is the system latency? Question 2: (Interrupts) Write the C code to define an ISR that handles UART1 peripheral interrupt on the Teensy 3.2. If you enable an interrupt in your C code, but don't define the ISR, what code executes when the interrupt is triggered? According to the datasheet, Teensy 3.2 has 2 pin change interrupts, PCINTO and PCINT1, yet all I/O pins are "interruptable". Explain how each pin change is serviced with only 2 pin change interrupts and how different events (rising, falling etc.) are captured Suppose we have a program with two ISRs, ISRO (priority 0) and ISR1 (priority 1) defined below: int mainO a. b. c. d. while(1) void isro0 _.disable_irq); I/disable interrupts do some stuff that takes 99 clock cycles .enableirq); I/ enable interrupts void isr10 _disable_irq) / disable interrupts do some stuff that takes 142 clock cycles .enable.irq); // enable interrupts If the datasheet states the interrupt latency is 15 cycles and nested interrupts are not supported, what is the system latency

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts