Question: Question 2 - Multi - level Paging ( 2 5 points ) ( This question is related to ILO 2 b - describe the principles

Question Multilevel Paging points

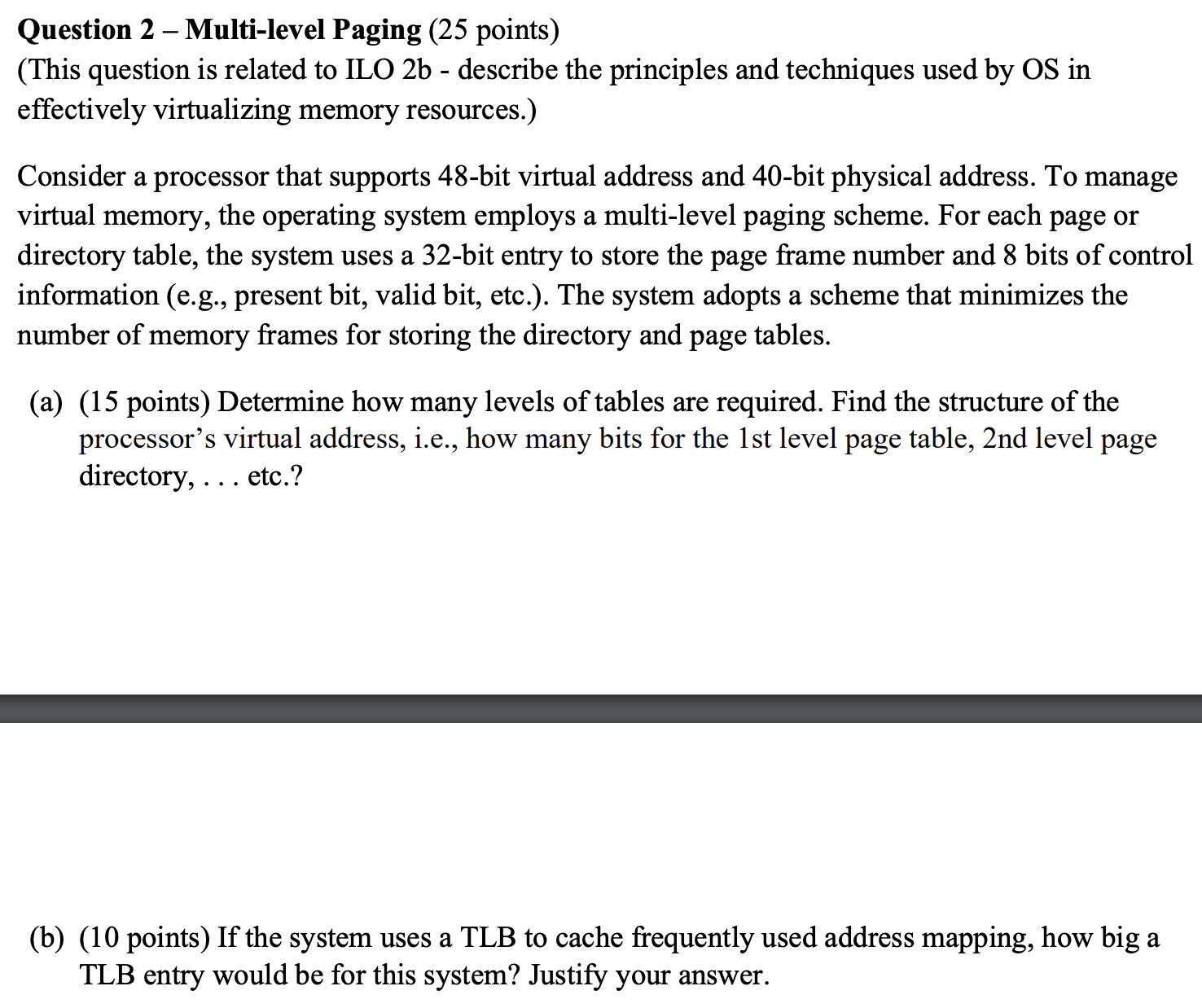

This question is related to ILO b describe the principles and techniques used by OS in effectively virtualizing memory resources.

Consider a processor that supports bit virtual address and bit physical address. To manage virtual memory, the operating system employs a multilevel paging scheme. For each page or directory table, the system uses a bit entry to store the page frame number and bits of control information eg present bit, valid bit, etc. The system adopts a scheme that minimizes the number of memory frames for storing the directory and page tables.

a points Determine how many levels of tables are required. Find the structure of the processor's virtual address, ie how many bits for the st level page table, nd level page directory, etc.?

b points If the system uses a TLB to cache frequently used address mapping, how big a TLB entry would be for this system? Justify your answer.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock