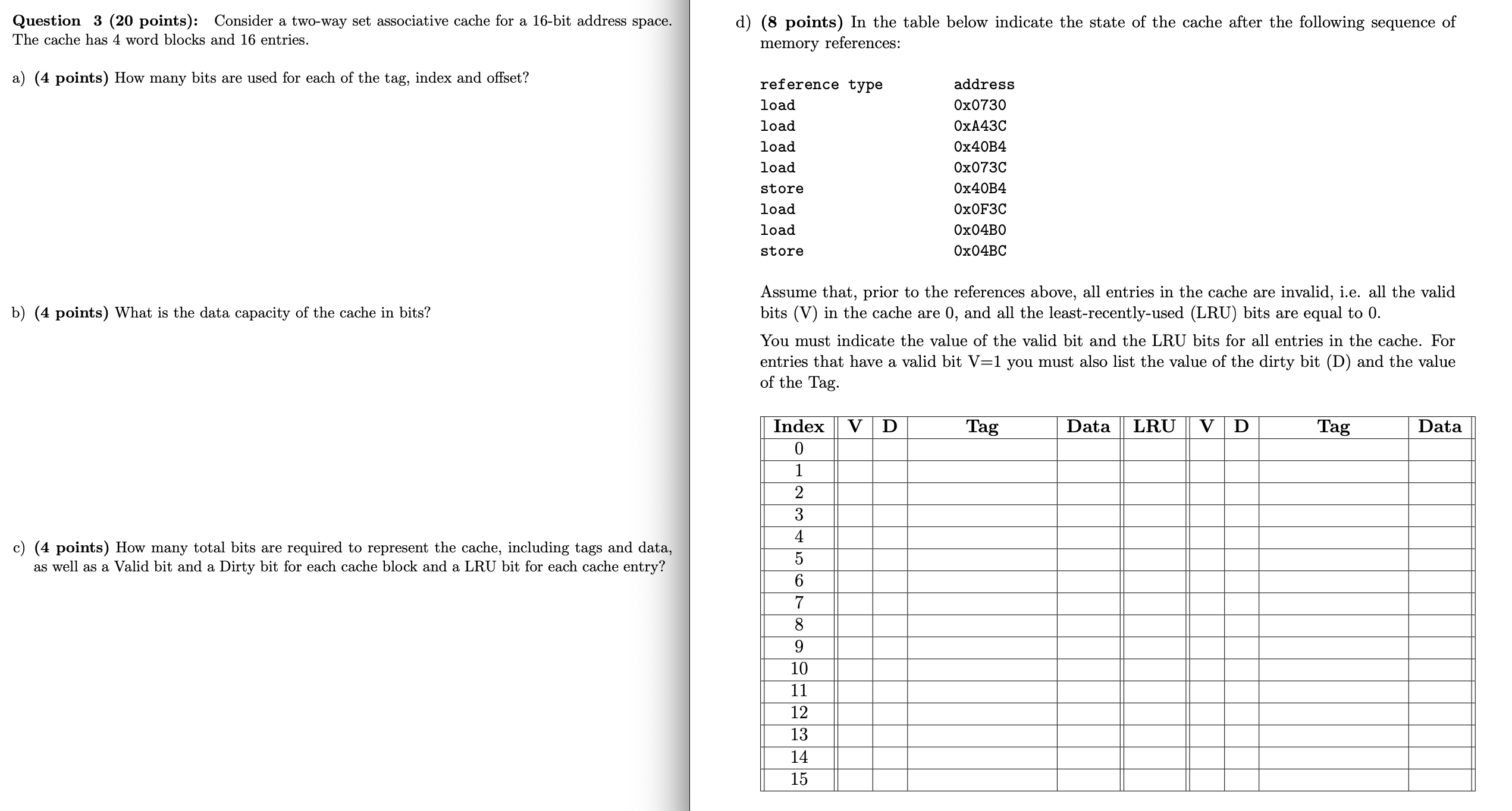

Question: Question 3 ( 2 0 points ) : Consider a two - way set associative cache for a 1 6 - bit address space. The

Question points: Consider a twoway set associative cache for a bit address space.

The cache has word blocks and entries.

a points How many bits are used for each of the tag, index and offset?

b points What is the data capacity of the cache in bits?

c points How many total bits are required to represent the cache, including tags and data,

as well as a Valid bit and a Dirty bit for each cache block and a LRU bit for each cache entry?

d points In the table below indicate the state of the cache after the following sequence of

memory references:

Assume that, prior to the references above, all entries in the cache are invalid, ie all the valid

bits V in the cache are and all the leastrecentlyused LRU bits are equal to

You must indicate the value of the valid bit and the LRU bits for all entries in the cache. For

entries that have a valid bit you must also list the value of the dirty bit D and the value

of the Tag.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock