Question: Question # 3 ( computer architecture ) Let's consider dynamic scheduling. Consider a microarchitecture as shown in figure below. Assume that the arithmetic -

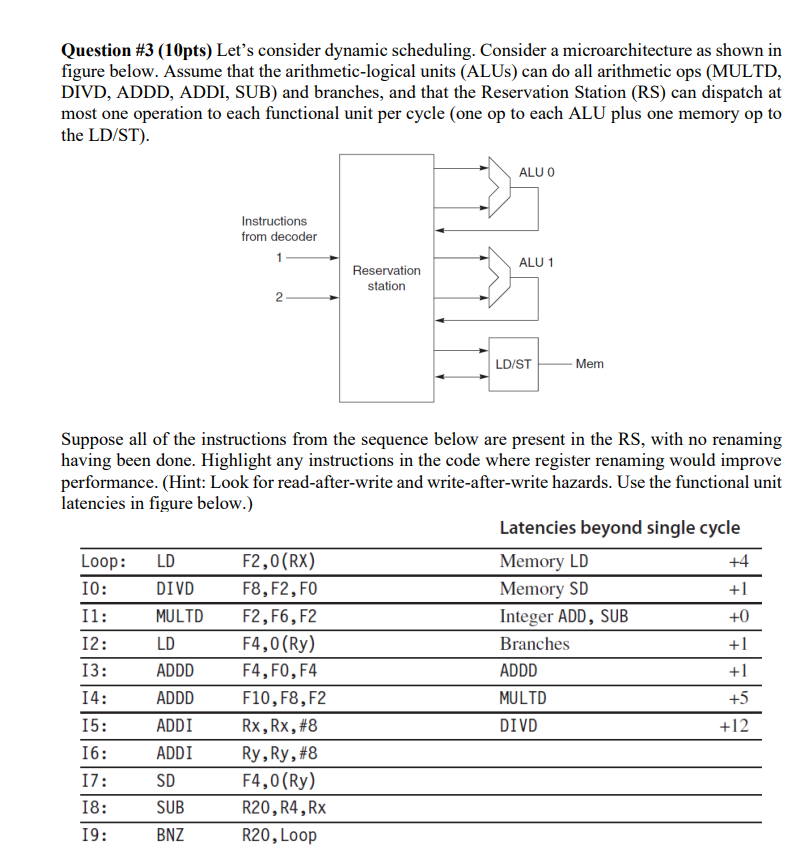

Question #computer architecture Let's consider dynamic scheduling. Consider a microarchitecture as shown in figure below. Assume that the arithmeticlogical units ALUs can do all arithmetic ops MULTD DIVD, ADDD, ADDI, SUB and branches, and that the Reservation Station RS can dispatch at most one operation to each functional unit per cycle one op to each ALU plus one memory op to the LDST

Suppose all of the instructions from the sequence below are present in the RS with no renaming having been done. Highlight any instructions in the code where register renaming would improve performance. Hint: Look for readafterwrite and writeafterwrite hazards. Use the functional unit latencies in figure below.

Latencies beyond single cycle

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock