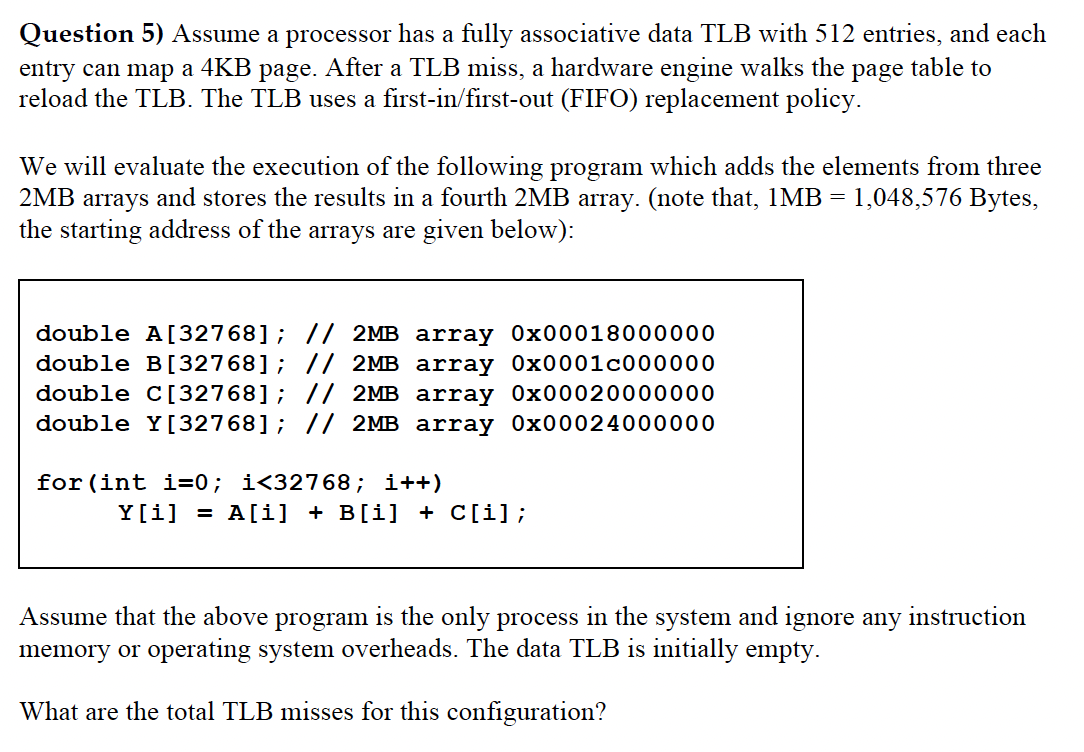

Question: Question 5 ) Assume a processor has a fully associative data TLB with 5 1 2 entries, and each entry can map a 4 K

Question Assume a processor has a fully associative data TLB with entries, and each

entry can map a page. After a TLB miss, a hardware engine walks the page table to

reload the TLB The TLB uses a firstinfirstout FIFO replacement policy.

We will evaluate the execution of the following program which adds the elements from three

arrays and stores the results in a fourth array. note that, Bytes,

the starting address of the arrays are given below:

Assume that the above program is the only process in the system and ignore any instruction

memory or operating system overheads. The data TLB is initially empty.

What are the total TLB misses for this configuration?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock