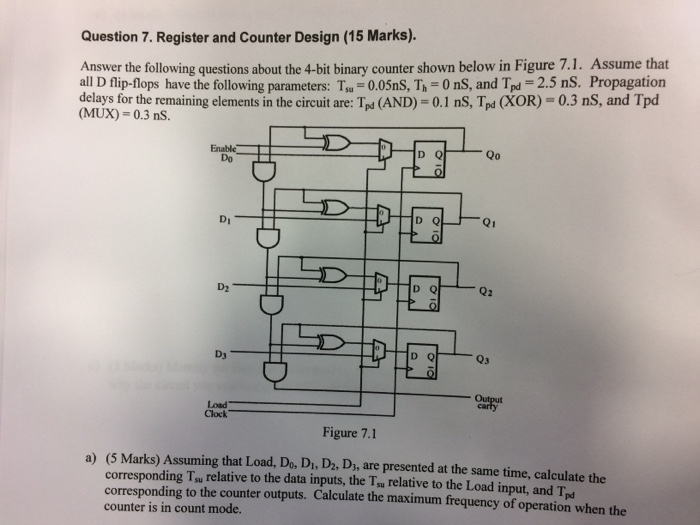

Question: Question 7. Register and counter Design (15 Marks). Answer the following questions about the 4-bit binary counter shown below in Figure 7.1. Assume that all

Question 7. Register and counter Design (15 Marks). Answer the following questions about the 4-bit binary counter shown below in Figure 7.1. Assume that all Dflip-flops have the following parameters: T 0.05ns, Th 0 nS, and TPd 2.5 ns. Propagation for the remaining elements in the circuit are: TP (AND-0.1 nS, TPd (XOR)"0.3 ns, and Tpd (MUX) 0.3 Qo Di D, D Q Q2 Figure 7.1 a) (5 Marks) Assuming that Load, Do, Di, D2, Dy, are presented at the same time, calculate the corresponding Tsu relative to the data inputs, the Tsu relative to the Load input, and Ted corresponding to the counter outputs. Calculate the maximum frequency of operation when the counter is in count mode. Question 7. Register and counter Design (15 Marks). Answer the following questions about the 4-bit binary counter shown below in Figure 7.1. Assume that all Dflip-flops have the following parameters: T 0.05ns, Th 0 nS, and TPd 2.5 ns. Propagation for the remaining elements in the circuit are: TP (AND-0.1 nS, TPd (XOR)"0.3 ns, and Tpd (MUX) 0.3 Qo Di D, D Q Q2 Figure 7.1 a) (5 Marks) Assuming that Load, Do, Di, D2, Dy, are presented at the same time, calculate the corresponding Tsu relative to the data inputs, the Tsu relative to the Load input, and Ted corresponding to the counter outputs. Calculate the maximum frequency of operation when the counter is in count mode

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts