Question: Question 9 . ( 2 0 points ) - Spice Simulation Complete the following SRAM circuit optimization procedure. Submit your source codes of the HSpice

Question points Spice Simulation

Complete the following SRAM circuit optimization procedure. Submit your source codes of the HSpice netlist and stimulus, simulation results, and screenshots of your simulation.

Refer to the lab sessions Labs and and Lec and Lec

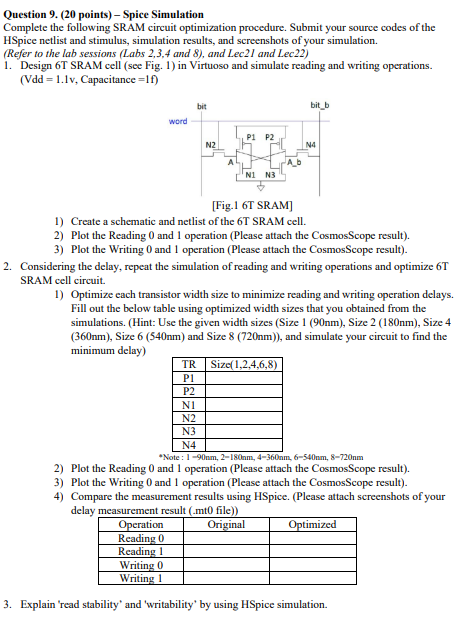

Design T SRAM cell see Fig. in Virtuoso and simulate reading and writing operations. Vdd mathrmv Capacitance mathrmf

Create a schematic and netlist of the T SRAM cell.

Plot the Reading and operation Please attach the CosmosScope result

Plot the Writing and operation Please attach the CosmosScope result

Considering the delay, repeat the simulation of reading and writing operations and optimize T SRAM cell circuit.

Optimize each transistor width size to minimize reading and writing operation delays. Fill out the below table using optimized width sizes that you obtained from the simulations. Hint: Use the given width sizes Size nm Size nm Size mathrm~nm Size mathrm~nm and Size mathrm~nm and simulate your circuit to find the minimum delay

Note: nmnmnmnmnm

Plot the Reading and operation Please attach the CosmosScope result

Plot the Writing and operation Please attach the CosmosScope result

Compare the measurement results using HSpice. Please attach screenshots of your delay measurement result mt file

Explain 'read stability' and 'writability' by using HSpice simulation.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock