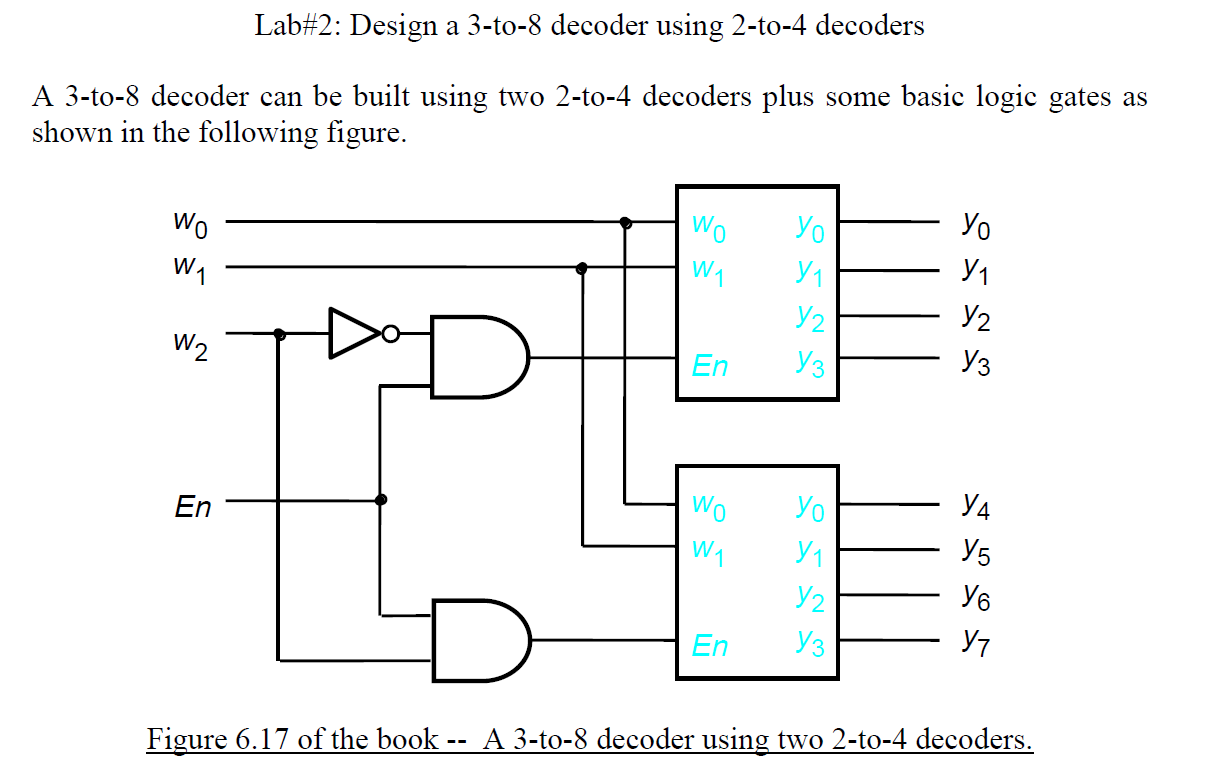

Question: Question on VHDL 3 to 8 decoder using two 2 to 4 decoders. Please help! I have successfully created the code for this problem using

Question on VHDL 3 to 8 decoder using two 2 to 4 decoders. Please help!

I have successfully created the code for this problem using port map dec2to4.

I'm having trouble with the test bench at the moment. It only gives me the input but the output is only empty.

Here is my code for dec3to8:

-----------------------------------------------------

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all;

entity dec3to8 is Port ( w : in STD_LOGIC_VECTOR (2 downto 0); EN : in STD_LOGIC; Y : out STD_LOGIC_VECTOR (7 downto 0)); end dec3to8;

architecture Behavioral of dec3to8 is

component dec2to4 is Port ( enable : in STD_LOGIC; sw : in STD_LOGIC_VECTOR (1 downto 0); led : out STD_LOGIC_VECTOR(3 downto 0)); end component;

signal m0: STD_LOGIC; signal m1: STD_LOGIC;

begin U1: dec2to4 Port map(m1,w(1 downto 0),Y(7 downto 4)); U2: dec2to4 Port map(m0,w(1 downto 0),Y(3 downto 0)); m0

end Behavioral;

-----------------------------------------------

code for dec2to4

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all;

entity dec2to4 is Port ( enable : in STD_LOGIC; sw : in STD_LOGIC_VECTOR (1 downto 0); led : out STD_LOGIC_VECTOR (3 downto 0)); end dec2to4;

architecture Behavioral of dec2to4 is

begin led

end Behavioral;

------------------------------------------------------------

Test Bench code:

LIBRARY ieee; USE ieee.std_logic_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --USE ieee.numeric_std.ALL; ENTITY dec3to8_testbench IS END dec3to8_testbench; ARCHITECTURE behavior OF dec3to8_testbench IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT dec3to8 IS PORT( w : IN std_logic_vector(2 downto 0); EN : IN std_logic; Y : OUT std_logic_vector(7 downto 0) ); END COMPONENT; --Inputs signal test_seq: std_logic_vector(3 downto 0):=(others => '0'); --Outputs signal Y : std_logic_vector(7 downto 0):=(others => '0'); BEGIN -- Instantiate the Unit Under Test (UUT) uut: dec3to8 PORT MAP ( w => test_seq(2 downto 0), EN => test_seq(3), Y => Y );

-- Stimulus process stim_proc: process begin test_seq

END;

----------------------------------------------

I need help with the test bench because it doesn't give the result I wanted. I'm not sure if there is something wrong with the orginal code but I tested them and they were all good

Thank you

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts