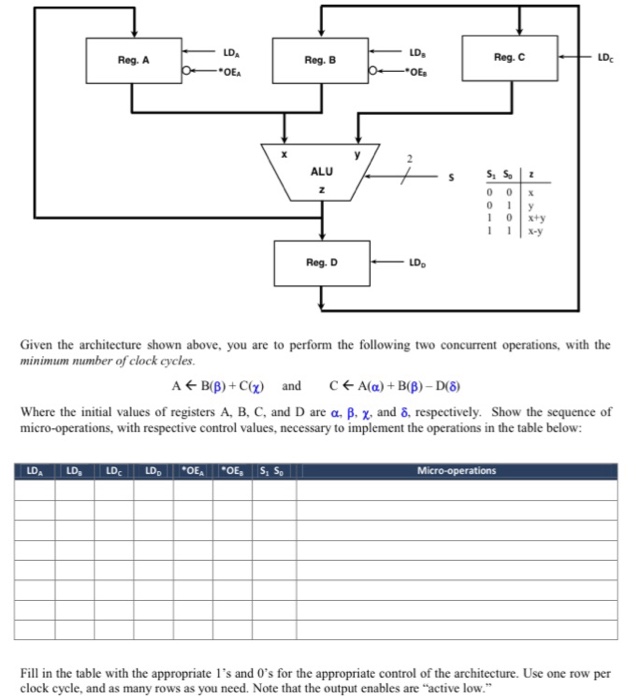

Question: Show every step! Thanks Reg. A LDA Reg. B LD Reg. C OEA ALU S, Sz | | x-y Reg. D LDD Given the architecture

Reg. A LDA Reg. B LD Reg. C OEA ALU S, Sz | | x-y Reg. D LDD Given the architecture shown above, you are to perform the following two concurrent operations, with the minimum number of clock cycles A Bip)+E(z) and C A(?) + B(?)-D(8) where the initial values of registers A, B, C, and D are o. ?.x and ?, respectively. Show the sequence of micro-operations, with respective control values, necessary to implement the operations in the table below Fill in the table with the appropriate 1's and O's for the appropriate control of the architecture. Use one row per clock cycle, and as many rows as you need. Note that the output enables are "active low." Reg. A LDA Reg. B LD Reg. C OEA ALU S, Sz | | x-y Reg. D LDD Given the architecture shown above, you are to perform the following two concurrent operations, with the minimum number of clock cycles A Bip)+E(z) and C A(?) + B(?)-D(8) where the initial values of registers A, B, C, and D are o. ?.x and ?, respectively. Show the sequence of micro-operations, with respective control values, necessary to implement the operations in the table below Fill in the table with the appropriate 1's and O's for the appropriate control of the architecture. Use one row per clock cycle, and as many rows as you need. Note that the output enables are "active low

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts