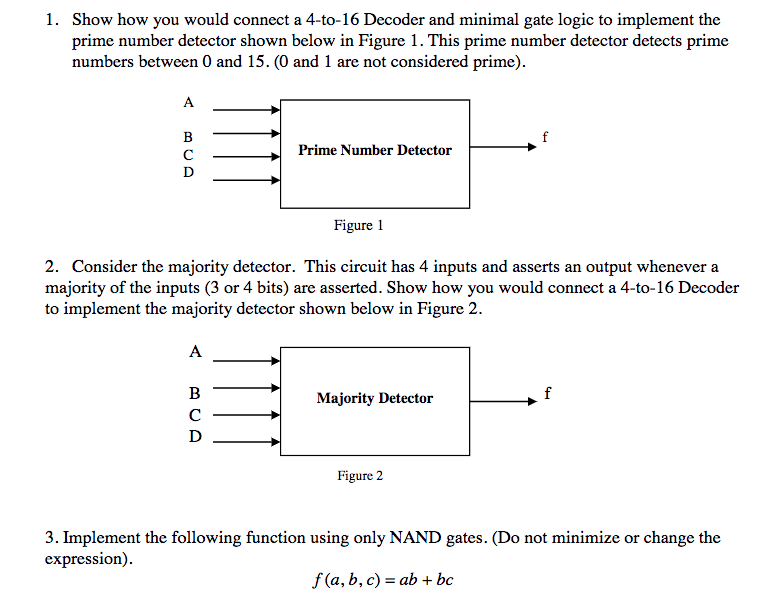

Question: Show how you would connect a 4-to-16 Decoder and minimal gate logic to implement the prime number detector shown below in Figure 1. This prime

Show how you would connect a 4-to-16 Decoder and minimal gate logic to implement the prime number detector shown below in Figure 1. This prime number detector detects prime numbers between 0 and 15. (0 and 1 are not considered prime) 1. CPrime Number Detector Figure 1 2. Consider the majority detector. This circuit has 4 inputs and asserts an output whenever a majority of the inputs (3 or 4 bits) are asserted. Show how you would connect a 4-to-16 Decoder to implement the majority detector shown below in Figure 2. Majority Detector Figure 2 3. Implement the following function using only NAND gates. (Do not minimize or change the expression) f(a, b, c)-ab+ bc

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts