Question: solution and explain why you solution like it specipclyyy q 2 Q 1 ) ( 1 4 points: ( 9 + 5 )

solution and explain why you solution like it specipclyyy q

Q points:

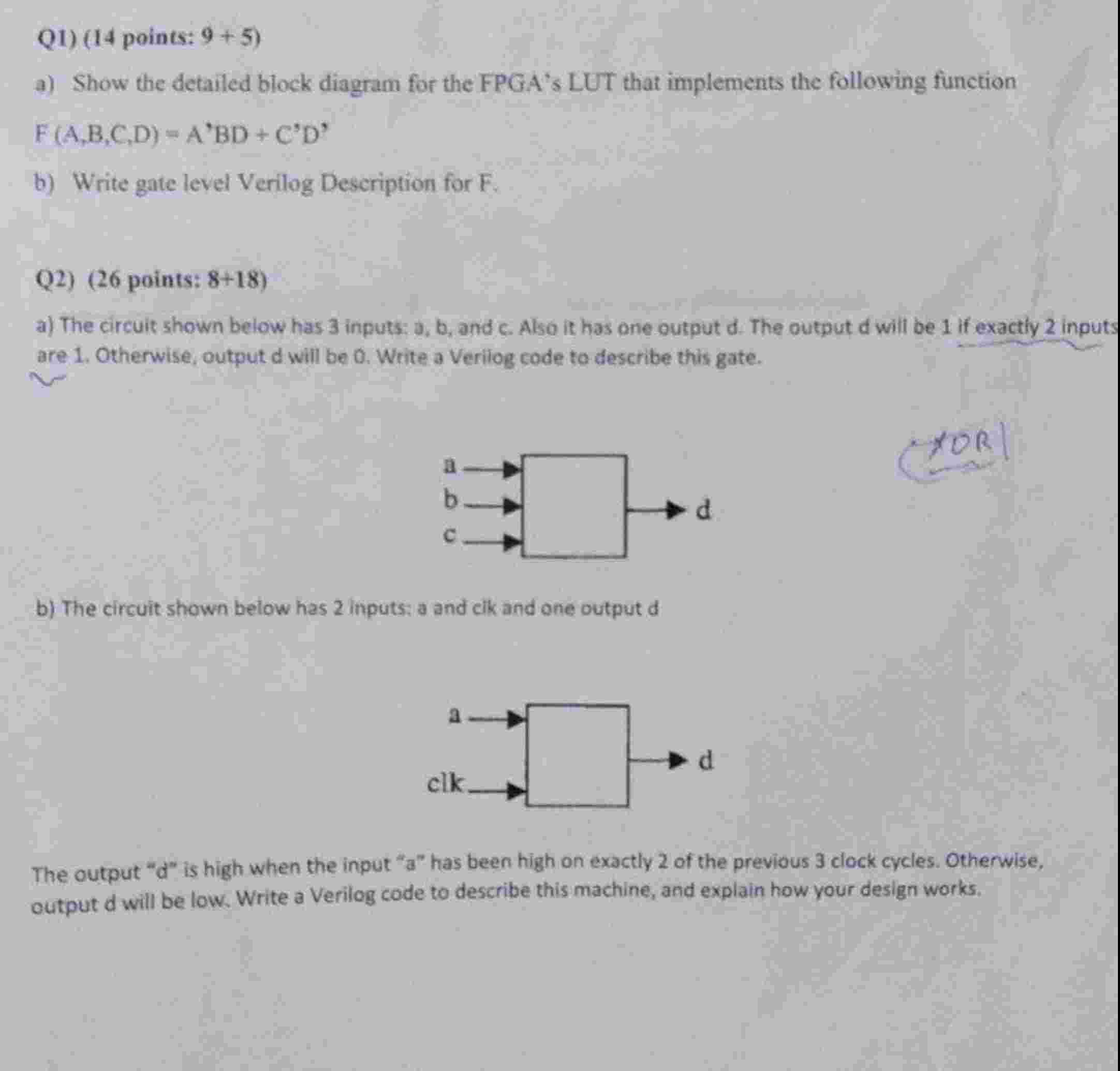

a Show the detailed block diagram for the FPGA's LUT that implements the following function

FA B C DAprime B DCprime Dprime

b Write gate level Verilog Description for F

Q points:

a The circuit shown below has inputs: a b and c Also it has one output d The output d will be if exactly inputs are Otherwise, output d will be Write a Verilog code to describe this gate.

b The circuit shown below has inputs: a and cik and one output d

The output d is high when the input a has been high on exactly of the previous clock cycles. Otherwise, output d will be low. Write a Verilog code to describe this machine, and explain how your design works.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock