Question: Suppose the original 32 bits DLX processor is modified to a accomplish floating-point operations disused in class as follows: If all in Integer R-type, I-Type,

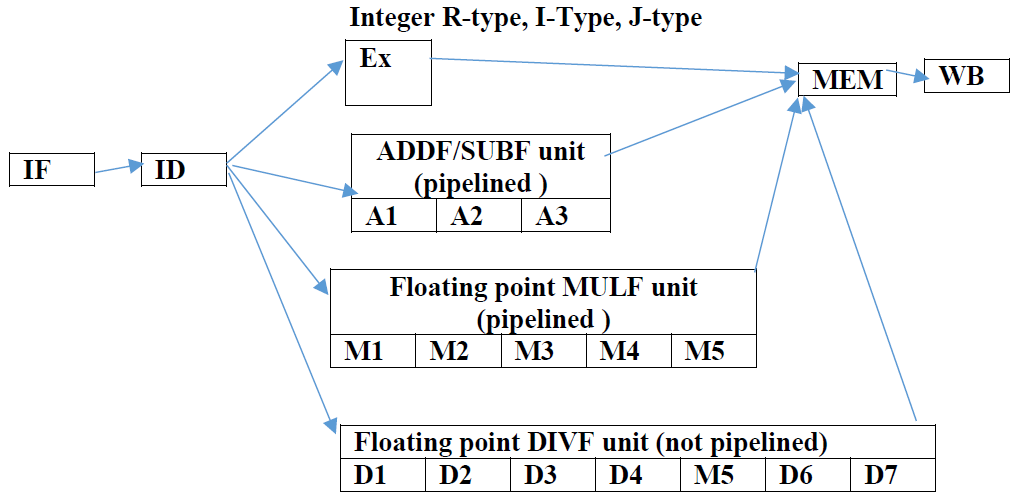

Suppose the original 32 bits DLX processor is modified to a accomplish floating-point operations disused in class as follows:

If all in Integer R-type, I-Type, J-type take one clock cycle in the EX phase, the ADDF/SUBF takes 3 clock cycles, MULF takes 5 clock cycles, DIVF takes 7 cycles. IF ADDF/SUBF, MULF units are internally pipelined and DIVF is not internally pipelined:

a) Show the execution of the following program: MULF R6, R2, R5 MULF R4, R8, R6 DIVF R8, R9, R2 DIVF R12, R15, R17 ADD R4, R5, R9 SUB R6, R2, R8 b) Repeat part (a) for the following instructions: DIVF R15, R9, R2 DIVF R12, R15, R17 MULF R8, R2, R15 MULF R4, R8, R6 ADD R4, R5, R9 SUB R6, R2, R8

IF Integer R-type, T-Type, J-type Ex MEM WB ADDF/SUBF unit (pipelined) A1 A2 A3 Floating point MULF unit (pipelined) M2 M3 M4 MS Floating point DIVF unit (not pipelined)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts