Question: Suppose you are trying to design a state machine which needs to take incoming data ( payload ) and provide an output packet with payload

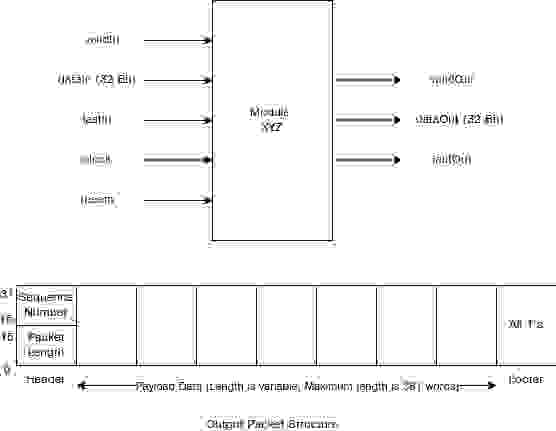

Suppose you are trying to design a state machine which needs to take incoming data payload and provide an output packet with payload data encapsulated between a Bit header and footer. The header format includes a bit payload length and bit Sequence Number count each incoming packet and assign the sequence number while the footer is static All s A packet of data is considered valid when data is provided with a valid as high, last signal indicates end of packet High for one clock cycle

Ports of your module would include,

Input: clock, resetn, dataIn, validIn, lastIn.

Output: dataOut, validOut, lastOut and any other signals you believe would help the design.

Kindly find below the attached diagram

Note: Maximum Packet Length is Words.

a Provide a state diagram which shows the transitions between each state required.

b A brief summary of what other components of the module should be provided besides the state machine. Write down the solution in the text box provided below

c Write an RTL Code and a Testbench for the same.

Please provide the state diagram from question a as a pdf attachment. Also, please include a screenshots of the simulation result showing clearly the input lines and output lines, if you have access to a Verilog simulator.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock