Question: suppose you have three different core designs which you can use to build a heterogeneous multi - core system. ( > ) An

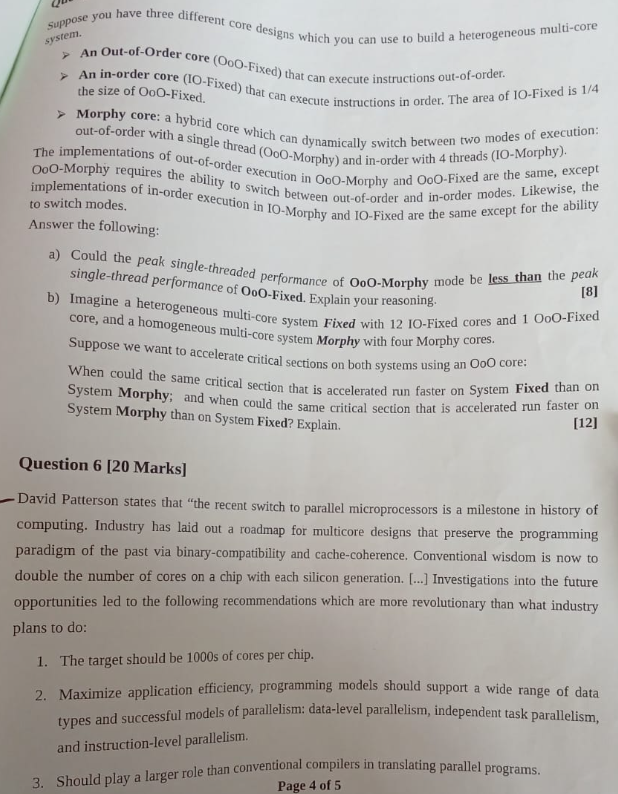

suppose you have three different core designs which you can use to build a heterogeneous multicore system.

An OutofOrder core mathrmOmathrmOFixed that can execute instructions outoforder.

An inorder core IOFixed that can execute instructions in order. The area of IOFixed is the size of OoOFixed.

Morphy core: a hybrid core which can dynamically switch between two modes of execution: outoforder with a single thread OoOMorphy and inorder with threads IOMorphy

The implementations of outoforder execution in OoOMorphy and OoOFixed are the same, except OoOMorphy requires the ability to switch between outoforder and inorder modes. Likewise, the implementations of inorder execution in IOMorphy and IOFixed are the same except for the ability to switch modes.

Answer the following:

a Could the peak singlethreaded performance of OoOMorphy mode be less than the peak singlethread performance of OoOFixed. Explain your reasoning.

b Imagine a heterogeneous multicore system Fixed with IOFixed cores and OoOFixed core, and a homogeneous multicore system Morphy with four Morphy cores.

Suppose we want to accelerate critical sections on both systems using an OoO core:

When could the same critical section that is accelerated run faster on System Fixed than on System Morphy; and when could the same critical section that is accelerated run faster on System Morphy than on System Fixed? Explain.

Question Marks

David Patterson states that "the recent switch to parallel microprocessors is a milestone in history of computing. Industry has laid out a roadmap for multicore designs that preserve the programming paradigm of the past via binarycompatibility and cachecoherence. Conventional wisdom is now to double the number of cores on a chip with each silicon generation. Investigations into the future opportunities led to the following recommendations which are more revolutionary than what industry plans to do:

The target should be s of cores per chip.

Maximize application efficiency, programming models should support a wide range of data types and successful models of parallelism: datalevel parallelism, independent task parallelism, and instructionlevel parallelism.

Should play a larger role than conventional compilers in translating parallel programs.

Page of

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock