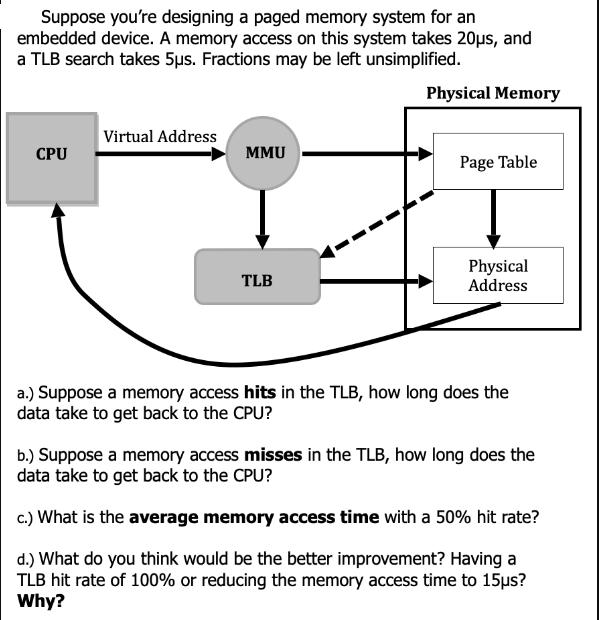

Question: Suppose you're designing a paged memory system for an embedded device. A memory access on this system takes 20s, and a TLB search takes

Suppose you're designing a paged memory system for an embedded device. A memory access on this system takes 20s, and a TLB search takes 5s. Fractions may be left unsimplified. CPU Virtual Address MMU TLB Physical Memory Page Table Physical Address a.) Suppose a memory access hits in the TLB, how long does the data take to get back to the CPU? b.) Suppose a memory access misses in the TLB, how long does the data take to get back to the CPU? c.) What is the average memory access time with a 50% hit rate? d.) What do you think would be the better improvement? Having a TLB hit rate of 100% or reducing the memory access time to 15s? Why?

Step by Step Solution

3.39 Rating (149 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts