Question: System Verilog in putty 5. [10 Points| priEnc Write a module priEnc.sv, which indicates the highest priori. The output z should indicate the position of

System Verilog in putty

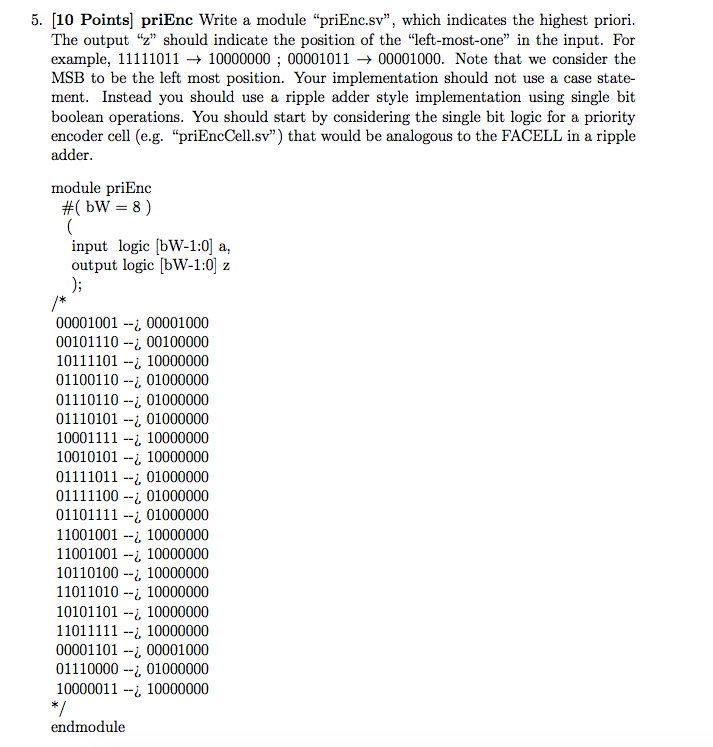

5. [10 Points| priEnc Write a module "priEnc.sv", which indicates the highest priori. The output "z" should indicate the position of the "left-most-one" in the input. For example, 11111011 10000000 ; 00001011 00001000" Note that we consider the MSB to be the left most position. Your implementation should not use a case state- ment. Instead you should use a ripple adder style implementation using single bit boolean operations. You should start by considering the single bit logic for a priority encoder cell (e.g. "priEncCell.sv") that would be analogous to the FACELL in a ripple adder module priEnc #( bw = 8 ) input logic [bW-1:0 a, output logic [bW-1:0 z 00001001-6 00001000 00101110-6 00100000 10111101 --i, 10000000 01100110-6 01000000 01110110-6 01000000 01110101-6 01000000 10001111 -l 10000000 10010101 --i, 10000000 01111011-6 01000000 01111100-6 01000000 01101111-6 01000000 11001001 -, 10000000 11001001 --i, 10000000 10110100- 10000000 11011010 -i 10000000 10101101 --i, 10000000 11011111 -, 10000000 00001101-6 00001000 01110000-6 01000000 10000011 --i, 10000000 endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts