Question: Tania Architecture, a RISC computer, has separate IM and DM . This architecture supports 1 0 0 different instructions of fixed - length opcodes. Here

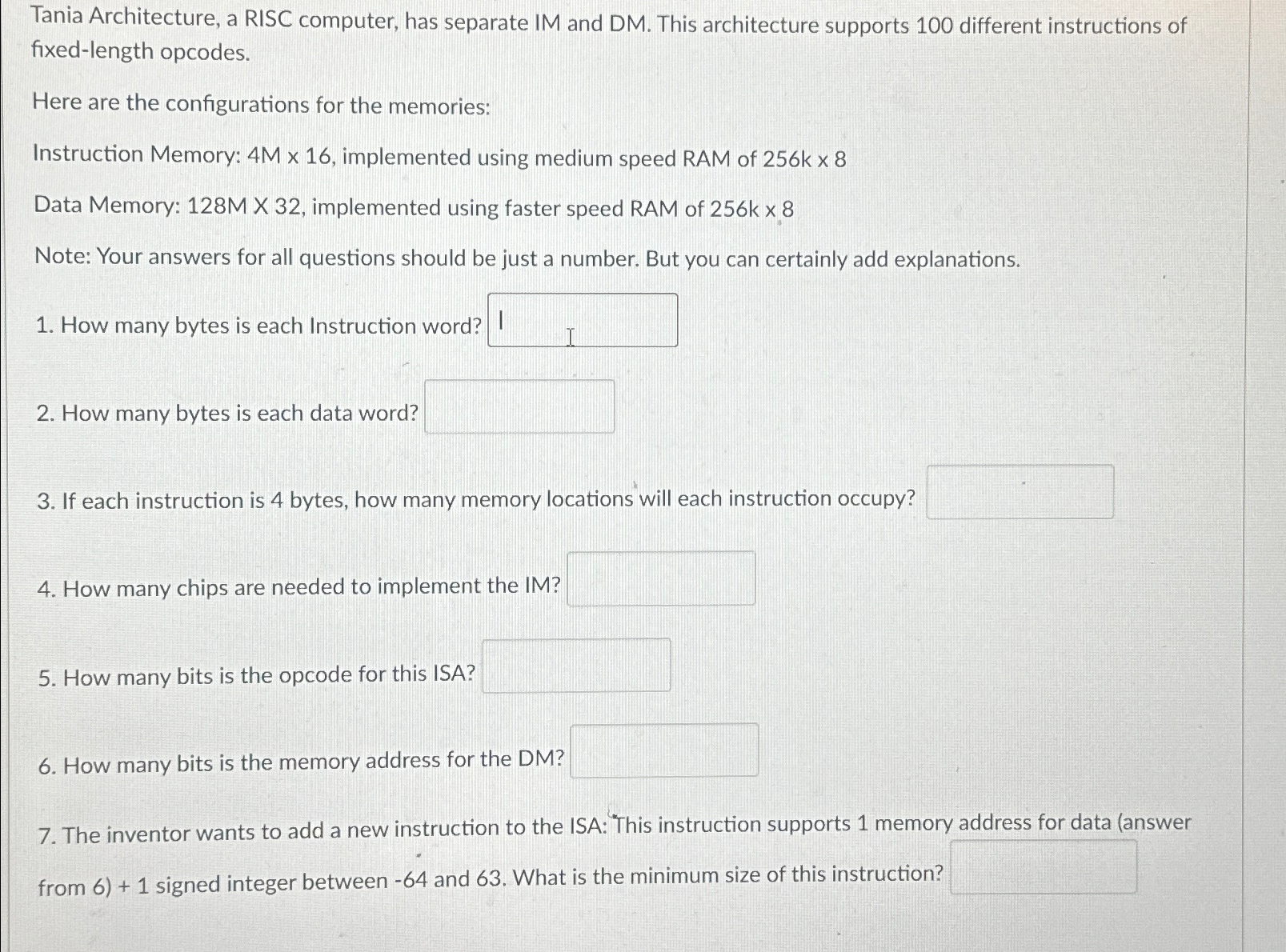

Tania Architecture, a RISC computer, has separate IM and DM This architecture supports different instructions of fixedlength opcodes.

Here are the configurations for the memories:

Instruction Memory: M implemented using medium speed RAM of

Data Memory: implemented using faster speed RAM of

Note: Your answers for all questions should be just a number. But you can certainly add explanations.

How many bytes is each Instruction word?

How many bytes is each data word?

If each instruction is bytes, how many memory locations will each instruction occupy?

How many chips are needed to implement the IM

How many bits is the opcode for this ISA?

How many bits is the memory address for the DM

The inventor wants to add a new instruction to the ISA: This instruction supports memory address for data answer from signed integer between and What is the minimum size of this instruction?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock