Question: tFigure 4.3.1 has a sample VHDL code for a D type latch. The process stateme senstih achitecture of the latch is a keyword. It is

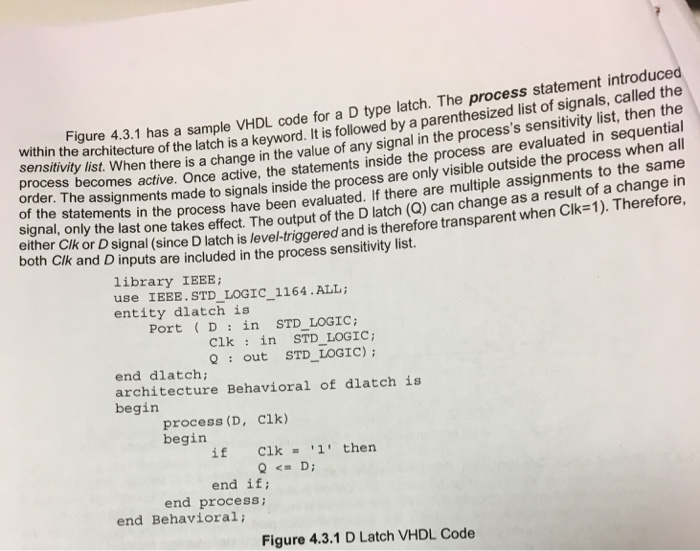

tFigure 4.3.1 has a sample VHDL code for a D type latch. The process stateme senstih achitecture of the latch is a keyword. It is followed by a parenthesized list of signals, ca change in the value of any signal in the process's sensitivity list, then the ss are evaluated in sequential sensitivi When there is a neassignments made to signals inside the process are only visible outside the process when all statements in the process have been evaluated. If there are multiple assignments to the same process becomes active order. The of the th last one takes effect. The output of the D latch (Q) can change as a result of a change in odbsignal (since D latch is level-triggered and is therefore transparent when Clk-1). Therefore, both both Clk and D inputs are included in the process sensitivity list. library IEEE; use IEEE. STD LOGIC 1164.ALL entity dlatch is Port D in STD_LOGIC; Clk in STD LOGIC; Qout STD_LOGIC) end dlatch; architecture Behavioral of dlatch is begin process (D, Clk) begin if Clk='1' then end if end process end Behavioral; Figure 4.3.1 D Latch VHDL Code

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts