Question: The answers are given. Please explain the process. Please start at 4.4. 4. (3 points each) The 5 stages of executing a MIPS instruction are

The answers are given. Please explain the process. Please start at 4.4.

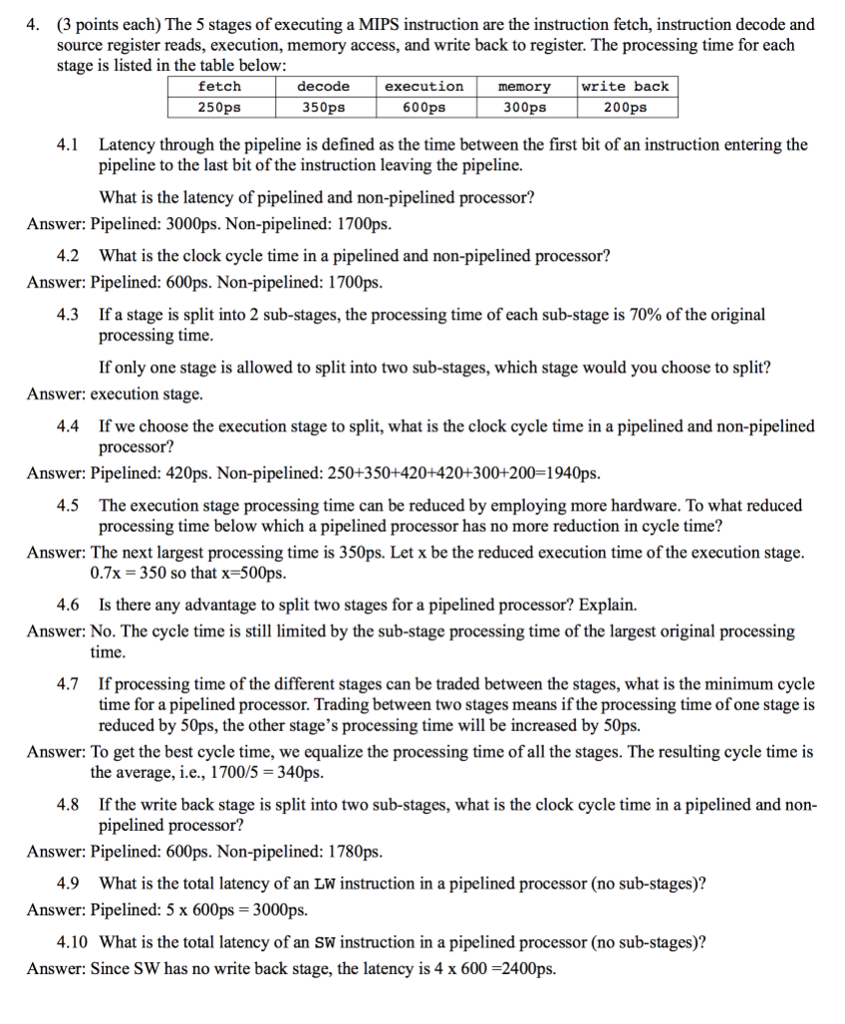

4. (3 points each) The 5 stages of executing a MIPS instruction are the instruction fetch, instruction decode and source register reads, execution, memory access, and write back to register. The processing time for each stage is listed in the table below fetch 250ps executionm memory write back 300ps decode 350ps 600ps 200ps 4.1 Latency through the pipeline is defined as the time between the first bit of an instruction entering the pipeline to the last bit of the instruction leaving the pipeline. What is the latency of pipelined and non-pipelined processor? What is the clock cycle time in a pipelined and If a stage is split into 2 sub-stages, the processing time of each sub-stage is 70% of the original Answer: Pipelined: 3000ps. Non-pipelined: 1700ps. 4.2 non-pipelined processor? Answer: Pipelined: 600ps. Non-pipelined: 1700ps. 4.3 processing time. If only one stage is allowed to split into two sub-stages, which stage would you choose to split? Answer: execution stage 4.4 If we choose the execution stage to split, what is the clock cycle time in a pipelined and non-pipelined processor? Answer: Pipelined: 420ps. Non-pipelined: 250+350+420+420+300+200-1940ps 4.5 The execution stage processing time can be reduced by employing more hardware. To what reduced processing time below which a pipelined processor has no more reduction in cycle time? Answer: The next largest processing time is 350ps. Let x be the reduced execution time of the execution stage. 0.7x 350 so that x-500ps 4.6 Is there any advantage to split two stages for a pipelined processor? Explain. Answer: No. The cycle time is still limited by the sub-stage processing time of the largest original processing time 4.7 If processing time of the different stages can be traded between the stages, what is the minimum cycle time for a pipelined processor. Trading between two stages means if the processing time of one stage is reduced by 50ps, the other stage's processing time will be increased by 50ps. the average, i.e., 1700/5-340ps. If the write back stage is split into two sub-stages, what is the clock cycle time in a pipelined and non- Answer: To get the best cycle time, we equalize the processing time of all the stages. The resulting cycle time is 4.8 pipelined processor? Answer: Pipelined: 600ps. Non-pipelined: 1780ps. 4.9 What is the total latency of an LW instruction in a pipelined processor (no sub-stages)? Answer: Pipelined: 5 x 600ps- 3000ps. 4.10 What is the total latency of an SW instruction in a pipelined processor (no sub-stages)? Answer: Since SW has no write back stage, the latency is 4 x 600 -2400ps

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts