Question: The code below is for a seven segment display that is working along side a frequency divider and a counter. I need help in storing

The code below is for a seven segment display that is working along side a frequency divider and a counter. I need help in storing data from the highlighted portion of the 4 bit register to then displaying it

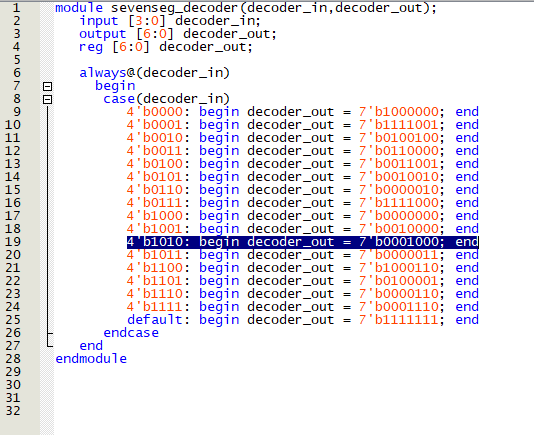

Seven Segment

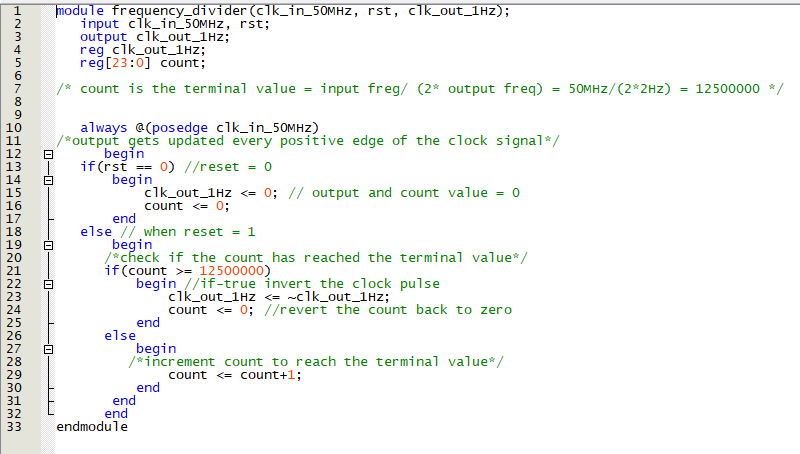

Divider

8 9 10 11 12 13 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 module sevenseg_decoder (decoder_in, decoder_out); input [3:0) decoder_in; output [6:0] decoder _out; reg [6:0] decoder_out; always@(decoder_in) begin case(decoder-in) 4'boooo: begin decoder_out = 7'b1000000; end 4b0001: begin decoder _out = 7'b1111001; end 4'b0010: begin decoder _out = 7'b0100100; end 4'b0011: begin decoder_out = 7'60110000; end 4'50100: begin decoder_out = 7'60011001; end 4'b0101: begin decoder _out 7'b0010010; end 4'b0110: begin decoder _out = 7'b0000010; end 4'b0111: begin decoder _out = 7'b1111000; end 4'b1000: begin decoder_out = 7'b0000000; end 4'b1001: begin decoder_out = 7 'b0010000; end 4 b1010: begin decoder_out = 7 b0001000; end 4 61011: begin decoder _out = 7'b0000011; end 4'b1100: begin decoder _out = 7'b1000110; end 4'b1101: begin decoder _out = 7'b0100001; end 4'b1110: begin decoder _out = 7'b0000110; end 4'b1111: begin decoder _out 7'b0001110; end default: begin decoder _out = 7'b1111111; end endcase end endmodule 1 2 module frequency_divider (clk_in_50MHz, rst, clk_out_1Hz); input cik_in_50MHz, rst; output clk_out_1Hz; reg clk_out_1Hz; reg[23:0] count; /* count is the terminal value = input freg/ (2* output freq) = 50MHZ/(2*2H2) = 12500000 */ 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 = 1 A always a(posedge clk_in_50MHZ) /*output gets updated every positive edge of the clock signal/ begin if(rst == 0) //reset = 0 begin clk_out_1Hz = 12500000) begin //if-true invert the clock pulse clk_out_1Hz = 12500000) begin //if-true invert the clock pulse clk_out_1Hz

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts