Question: The following code segment is to be executed on a RISC processor with: 1: R1 R2 + R3 2: R4 R1 + R2 3:

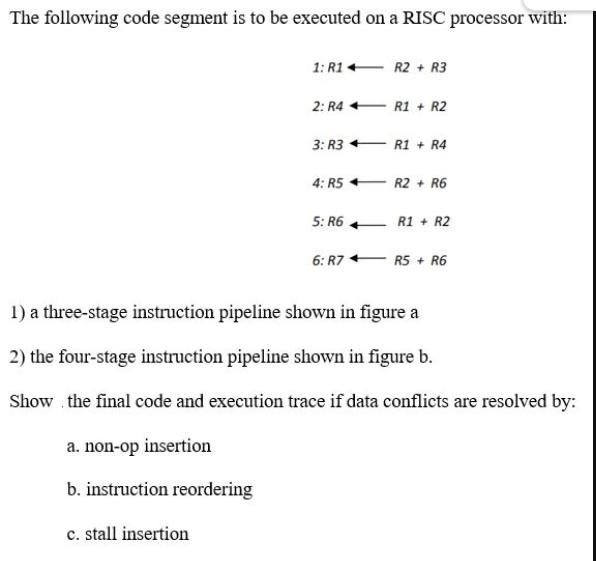

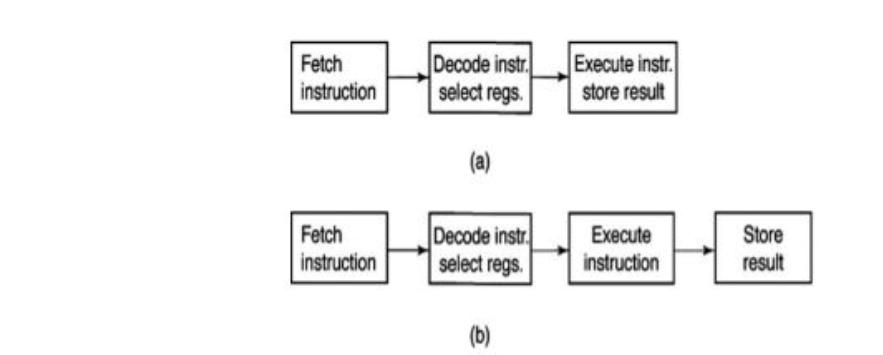

The following code segment is to be executed on a RISC processor with: 1: R1 R2 + R3 2: R4 R1 + R2 3: R3+ R1 + R4 4: R5 -R2R6 5: R6 R1 + R2 6: R7 R5+ R6 1) a three-stage instruction pipeline shown in figure a 2) the four-stage instruction pipeline shown in figure b. Show the final code and execution trace if data conflicts are resolved by: a. non-op insertion b. instruction reordering c. stall insertion Fetch instruction Decode instr select regs. Execute instr. store result (a) Fetch Decode instr Execute Store instruction select regs. instruction result (b)

Step by Step Solution

There are 3 Steps involved in it

To handle data conflicts in a pipeline there are several techniques that can be used such as nonoperation NOP insertion instruction reordering and sta... View full answer

Get step-by-step solutions from verified subject matter experts