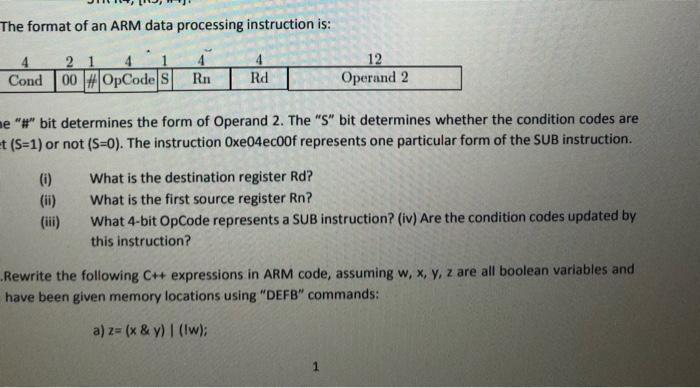

Question: The format of an ARM data processing instruction is: 21 4 Cond 00 OpCode S 12 Operand 2 Rn Rd ne# bit determines the form

The format of an ARM data processing instruction is: 21 4 Cond 00 OpCode S 12 Operand 2 Rn Rd ne"#" bit determines the form of Operand 2. The "S" bit determines whether the condition codes are et (S-1) or not (S=0). The instruction Oxe04ecoof represents one particular form of the SUB instruction. (0) What is the destination register Rd? What is the first source register Rn? What 4-bit OpCode represents a SUB instruction? (iv) Are the condition codes updated by this instruction? Rewrite the following C++ expressions in ARM code, assuming w, x, y, z are all boolean variables and have been given memory locations using "DEFB" commands: a) z= (x & y) I (w); The format of an ARM data processing instruction is: 21 4 Cond 00 OpCode S 12 Operand 2 Rn Rd ne"#" bit determines the form of Operand 2. The "S" bit determines whether the condition codes are et (S-1) or not (S=0). The instruction Oxe04ecoof represents one particular form of the SUB instruction. (0) What is the destination register Rd? What is the first source register Rn? What 4-bit OpCode represents a SUB instruction? (iv) Are the condition codes updated by this instruction? Rewrite the following C++ expressions in ARM code, assuming w, x, y, z are all boolean variables and have been given memory locations using "DEFB" commands: a) z= (x & y) I (w)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts