Question: The memory controller on a microprocessor employs a limited open page policy, keeping pages open for a fixed amount of time after each access.

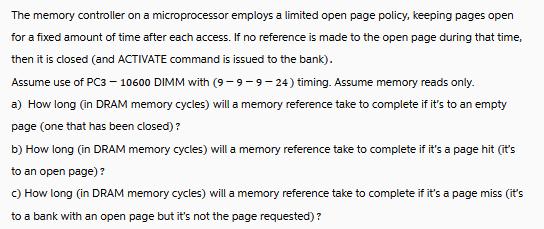

The memory controller on a microprocessor employs a limited open page policy, keeping pages open for a fixed amount of time after each access. If no reference is made to the open page during that time, then it is closed (and ACTIVATE command is issued to the bank). Assume use of PC3-10600 DIMM with (9-9-9-24) timing. Assume memory reads only. a) How long (in DRAM memory cycles) will a memory reference take to complete if it's to an empty page (one that has been closed)? b) How long (in DRAM memory cycles) will a memory reference take to complete if it's a page hit (it's to an open page)? c) How long (in DRAM memory cycles) will a memory reference take to complete if it's a page miss (it's to a bank with an open page but it's not the page requested)?

Step by Step Solution

There are 3 Steps involved in it

The information provided specifies the timing of a PC310600 DIMM with 99924 timing The numbers in pa... View full answer

Get step-by-step solutions from verified subject matter experts