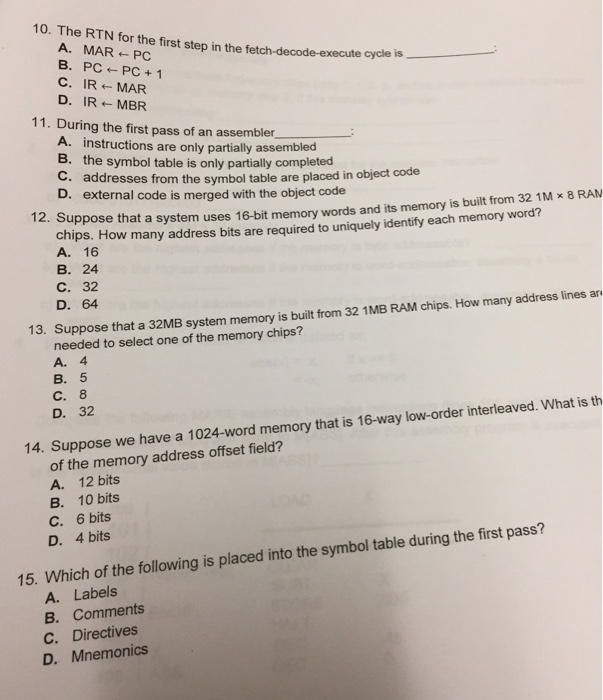

Question: The RTN for the first step in the fetch-decode-execute cycle is ___________. MAR leftarrow PC PC leftarrow PC + 1 IR leftarrow MAR IR leftarrow

The RTN for the first step in the fetch-decode-execute cycle is ___________. MAR leftarrow PC PC leftarrow PC + 1 IR leftarrow MAR IR leftarrow MBR During the first pass of an assembler _______. instructions are only partially assembled the symbol table is only partially completed addresses from the symbol table are placed in object code external code is merged with the object code Suppose that a system uses 16-bit memory words and its memory is built from 3 2 1M times 8 RAM chips. How many address bits are required to uniquely identify each memory word? 16 24 32 64 Suppose that a 32MB system memory is built from 32 1MB RAM chips. How many address lines needed to select one of the memory chips? 4 5 8 32 Suppose we have a 1024-word memory that is 16-way low-order interleaved. What is of the memory address offset field? 12 bits 10 bits 6 bits 4 bits Which of the following is placed into the symbol table during the first pass? Labels Comments Direct

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts