Question: The technical reference manual for the Cortex-A15 says that the GIC is memory-mapped. That is, the core processors use memory-mapped I/O to communicate with the

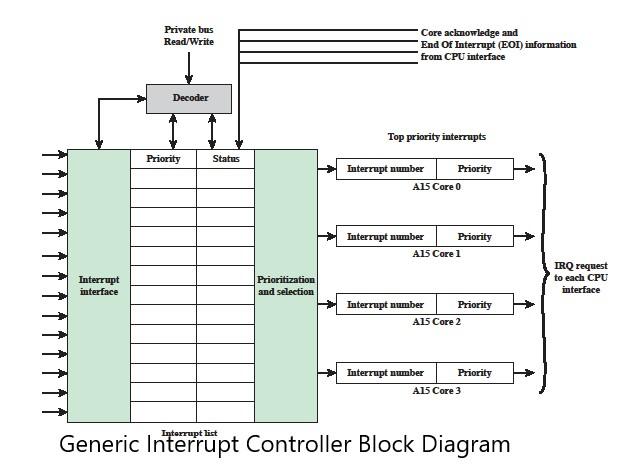

The technical reference manual for the Cortex-A15 says that the GIC is memory-mapped. That is, the core processors use memory-mapped I/O to communicate with the GIC. Recall from Chapter 7 that with memory-mapped I/O, there is a single address space for memory locations and I/O devices. The processor treats the status instructions to access both memory and I/O devices. Based on this information, what path through the block diagram below is used for the core processors to communicate with the GIC?

- Map this out in the diagram and submit

Private bus Read/Write Core acknowledge and End Of Interrupt (EOI) information from CPU interface Decoder Top priority interrupts Priority Status Interrupt number Priority A15 Core 0 Interrupt number Priority A15 Core 1 Interrupt interface Prioritization and selection IRQ request to each CPU interface Interrupt number Priority A15 Core 2 Interrupt number Priority A15 Care 3 Generic Interrupt Controller Block Diagram

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts