Question: The verilog module below implements a (buggy) priority encoder. Complete the truth table, using Xs where appropriate. (a) The Verilog module below implements a (buggy)

The verilog module below implements a (buggy) priority encoder. Complete the truth table, using Xs where appropriate.

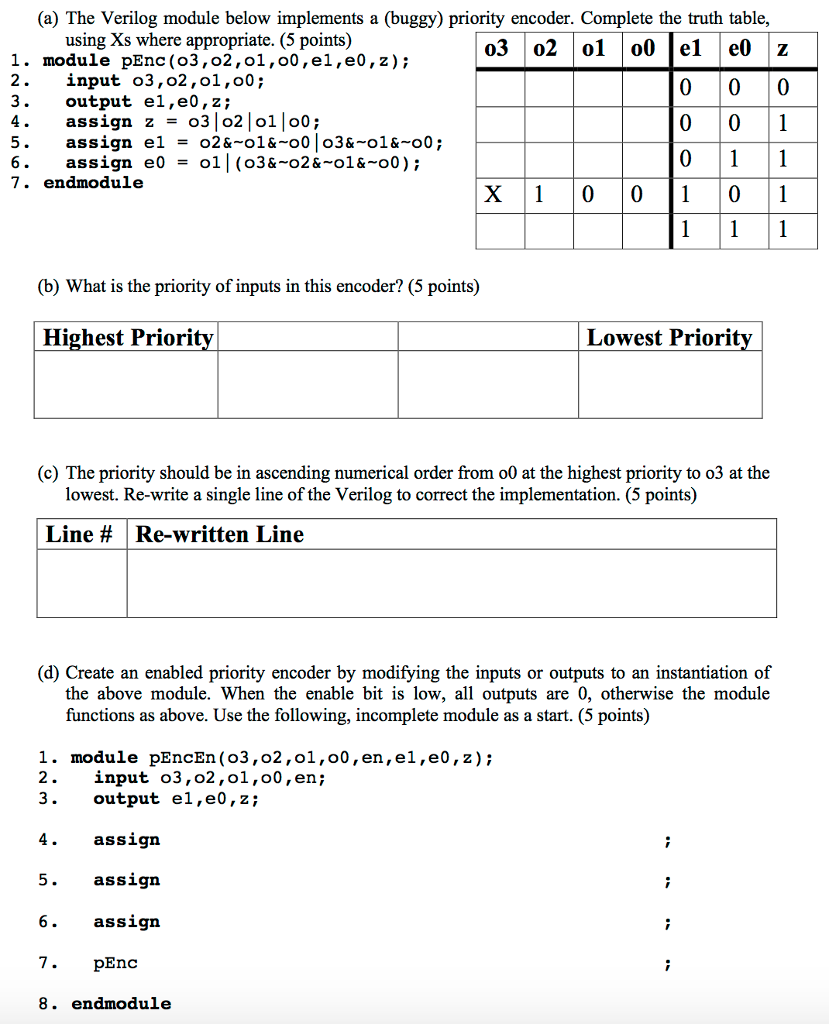

(a) The Verilog module below implements a (buggy) priority encoder. Complete the truth table, using Xs where appropriate. (5 points) 03 02olo0 lele0 z 1. module pEnc (o3,02,o1,00,e1,e0,z); 2.input o3,02,01,00; 3.output el,e0,z; 4. assign z= o3|02|01|00; 5. assign e1=o26-ola-ool o36-016-00; 6. assign e0=oll(o3a-o26-ola-oo); 7. endmodule X10 0 1 0 1 (b) What is the priority of inputs in this encoder? (5 points) Highest Priorit Lowest Priorit (c) The priority should be in ascending numerical order from o0 at the highest priority to o3 at the lowest. Re-write a single line of the Verilog to correct the implementation. (5 points) Line # Re-written Line (d) Create an enabled priority encoder by modifying the inputs or outputs to an instantiation of the above module. When the enable bit is low, all outputs are 0, otherwise the module functions as above. Use the following, incomplete module as a start. (5 points) 1. module pEncEn(o3,02,o1,00,en,el,e0,z); 2.input o3,02,o1,00,en; 3.output el,e0,z; 4. assign 5. assign 6. assign 7. pEnc 8. endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts