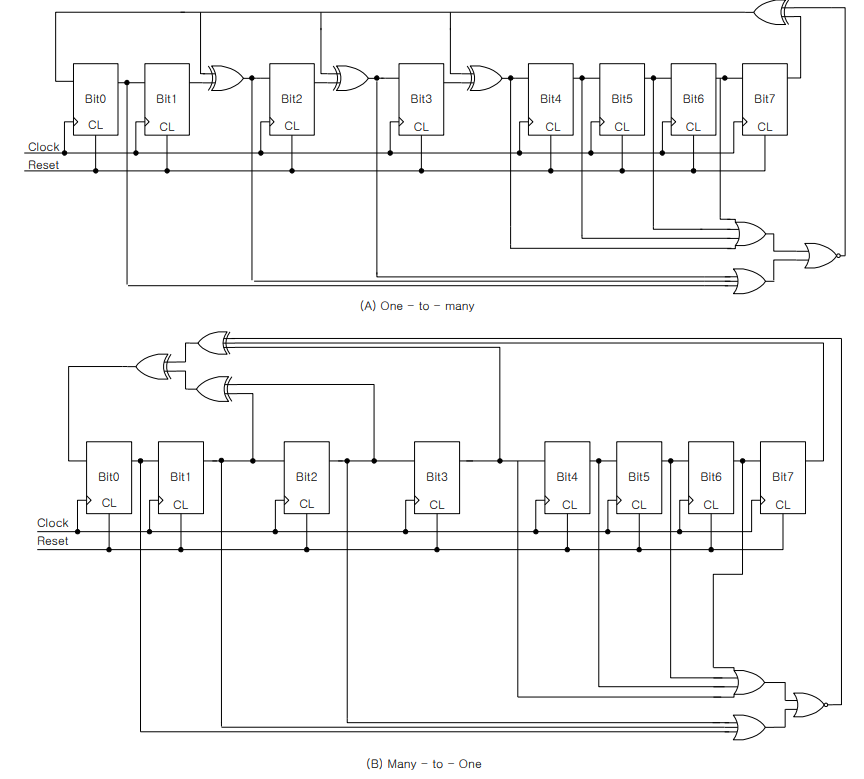

Question: These are picture ( A ) one - to - many n bit ( n = 8 ) LSFR Code. Please write picture ( B

These are picture A onetomany n bitnLSFR Code. Please write picture B manytoone n bitn LSFR verilog Code and test bench code. Please refer to the onetomany code and make it as similar as possible!!

picture A Verilog Code is this one.

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

: define TAPb

:

: define TAPS TAP

: module LFSRnbitClock Reset, Y;

: parameter Width ;

: input Clock, Reset;

: output Width : Y;

: wire Width : Taps;

: integer N;

: reg BitsNminusZero, Feedback;

: reg Width : LFSRReg, NextLFSRReg;

: assign TapsWidth :TAPS;

: always@negedge Reset or posedge Clock

: begin : LFSRRegister

: ifReset

: LFSRReg ;

: else

: LFSRReg NextLFSRReg;

: end

:

: always@LFSRReg

: begin : LFSRFeedback

:

: BitsNminusZero ~ LFSRRegWidth :;

: Feedback LFSRRegWidth BitsNminusZero;

:

: forNWidth;N;NN

: ifTapsN

:

: NextLFSRRegN LFSRRegN Feedback;

: else

: NextLFSRRegN LFSRRegN;

: NextLFSRReg Feedback;

: end

:

: assign Y LFSRReg;

: endmodule

And

: timescale nsns

: module tbLFSRnbit;

: reg Clock;

: reg Reset;

: wire : Y;

: LFSRnbit LFSRnbitClockClockResetResetYY;

: always # Clock~Clock;

: initial begin

: Reset; Clock;

: # Reset;

: # Reset;

: end

: endmoduleA One to many

B Many to One

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock