Question: These are verilog codes that simulate direct FIR filter and transpose FIR filter. When I simulated using the following code, TRAN _ out and DIRE

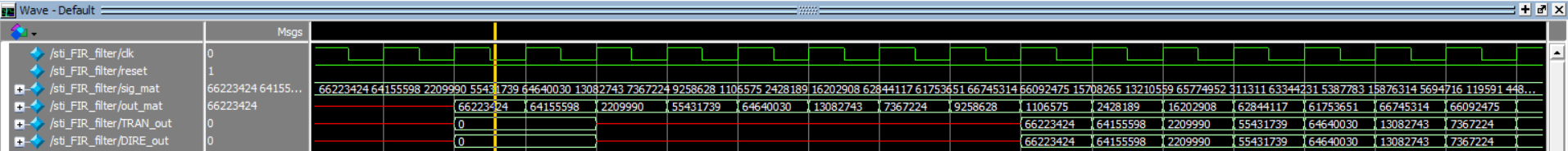

These are verilog codes that simulate direct FIR filter and transpose FIR filter. When I simulated using the following code, TRANout and DIREout are pushed out by ns compared to outmat as shown in the attached picture, resulting in an error.clock cyclens I tried using the delay using # properly outside and inside the door for, but I couldn't find the answer. Please let me know which part of the code should be modified.

timescale nsps

module stiFIRfilter;

reg clk reset;

reg : sigmat :;

reg : outmat;

reg : TRANout;

reg : DIREout;

wire : chaa ;

wire : ch;

wire : che;

wire : cha;

wire : ch;

wire : chcd;

topFIRfilter FIRclk reset, c c c c c c;

integer err;

initial

begin

clk ;

reset ;

#

reset ;

end

always # clk ~clk;

initial $readmemhinputvectorhex.txt FIR.DIRECTINPUTMEM.array; check the path of memory rocation module instance

initial $readmemhinputvectorhex.txt FIR.TRANSINPUTMEM.array; check the path of memory rocation module instance

integer i;

initial

begin

$readmemhoutputvectorhex.txt sigmat;

begin

#;

for i; i; ii

begin

outmat sigmati;

TRANout FIR.DIRECTOUTPUTMEM.arrayi;

DIREout FIR.TRANSOUTPUTMEM.arrayi;

ifTRANout outmatDIREout outmat err err ;

#;

end

$stop;

end

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock