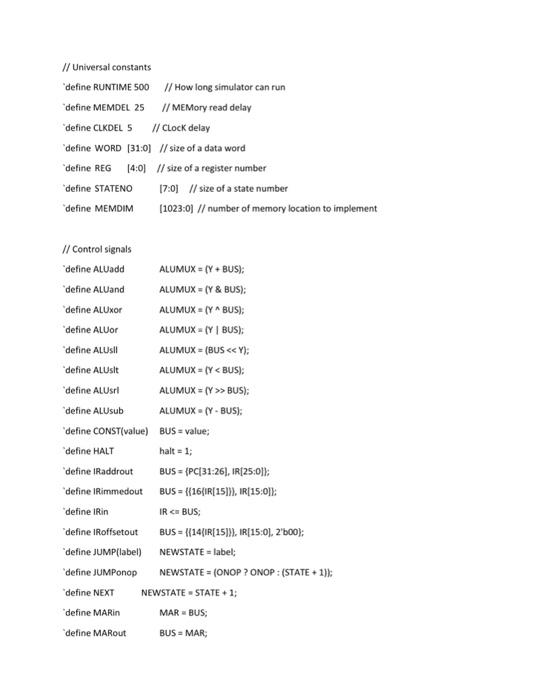

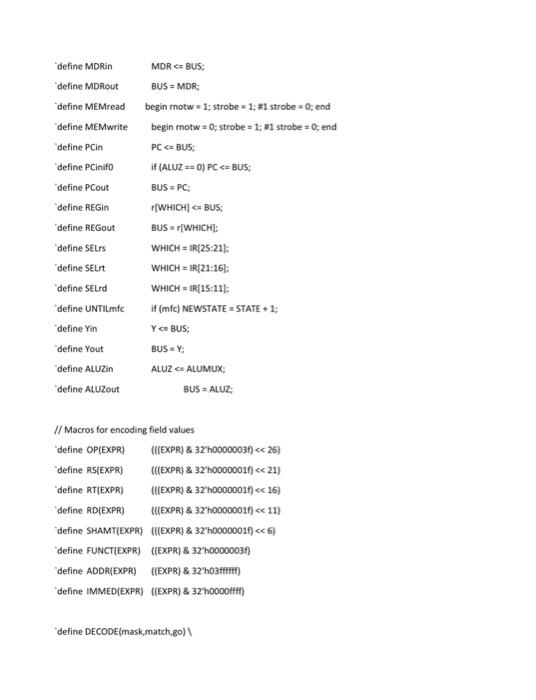

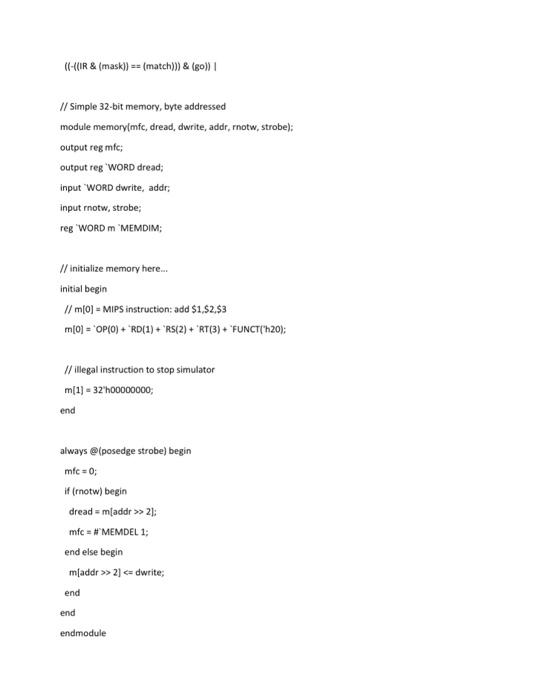

Question: This assignment is about modifying a verilog implementation of the multi-cycle design. // Universal constants 'define RUNTIME 500 // How long simulator can run 'define

![delay 'define WORD [31:0] // size of a data word 'define REG](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f50c70a1c14_53666f50c70807b0.jpg)

![[4:0]// size of a register number 'define STATENO [7:0] // size of](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f50c714ce4b_53666f50c70db347.jpg)

![a state number 'define MEMDIM [1023:0] // number of memory location to](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f50c71ef17e_53766f50c71895b0.jpg)

// Universal constants 'define RUNTIME 500 // How long simulator can run 'define MEMDEL 25 // MEMory read delay 'define CLKDEL 5 // CLock delay 'define WORD [31:0] // size of a data word 'define REG [4:0]// size of a register number 'define STATENO [7:0] // size of a state number 'define MEMDIM [1023:0] // number of memory location to implement // Control signals "define ALUadd ALUMUX = (Y + BUS); 'define ALUand ALUMUX = (Y \& BUS); 'define ALUxor ALUMUX =(Y BUS): "define AlUor ALUMUX = (Y | BUS): 'define ALUsll ALUMUX = (BUS Y); "define ALUslt ALUMUX = ( Y

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts