Question: This homework will make use of the MIPS assembly language, for which we are designing a small processor. The datapath of our small processor is

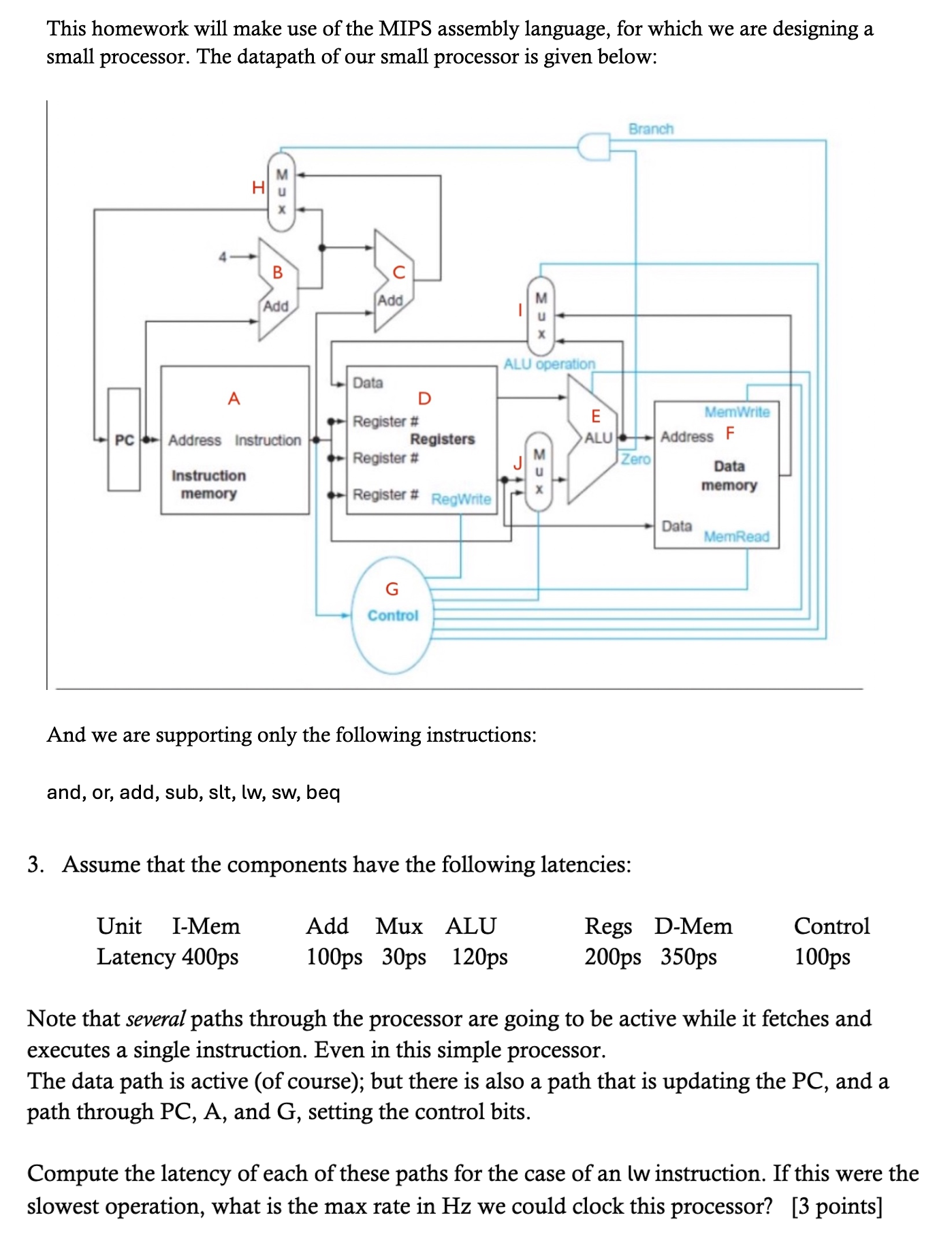

This homework will make use of the MIPS assembly language, for which we are designing a small processor. The datapath of our small processor is given below:

And we are supporting only the following instructions:

and, or add, sub, slt lw sw beq

Assume that the components have the following latencies:

tableUnit IMem,Add Mux,ALU,Regs,DMem,Control,Latency pspspspspspsps

Note that several paths through the processor are going to be active while it fetches and executes a single instruction. Even in this simple processor.

The data path is active of course; but there is also a path that is updating the PC and a path through PC A and G setting the control bits.

Compute the latency of each of these paths for the case of an Iw instruction. If this were the slowest operation, what is the max rate in we could clock this processor?

points

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock