Question: This presentation segment is booked for 5 0 minutes at the beginning of the day. Your actual content can be 2 0 - 2 5

This presentation segment is booked for minutes at the beginning of the day.

Your actual content can be minutes in length, the rest of the time will be

used in Q&A Your presentation topic is provided below, please do let us CCd to

this email know if you have any questions or if you need any clarifications once you

review the topic.

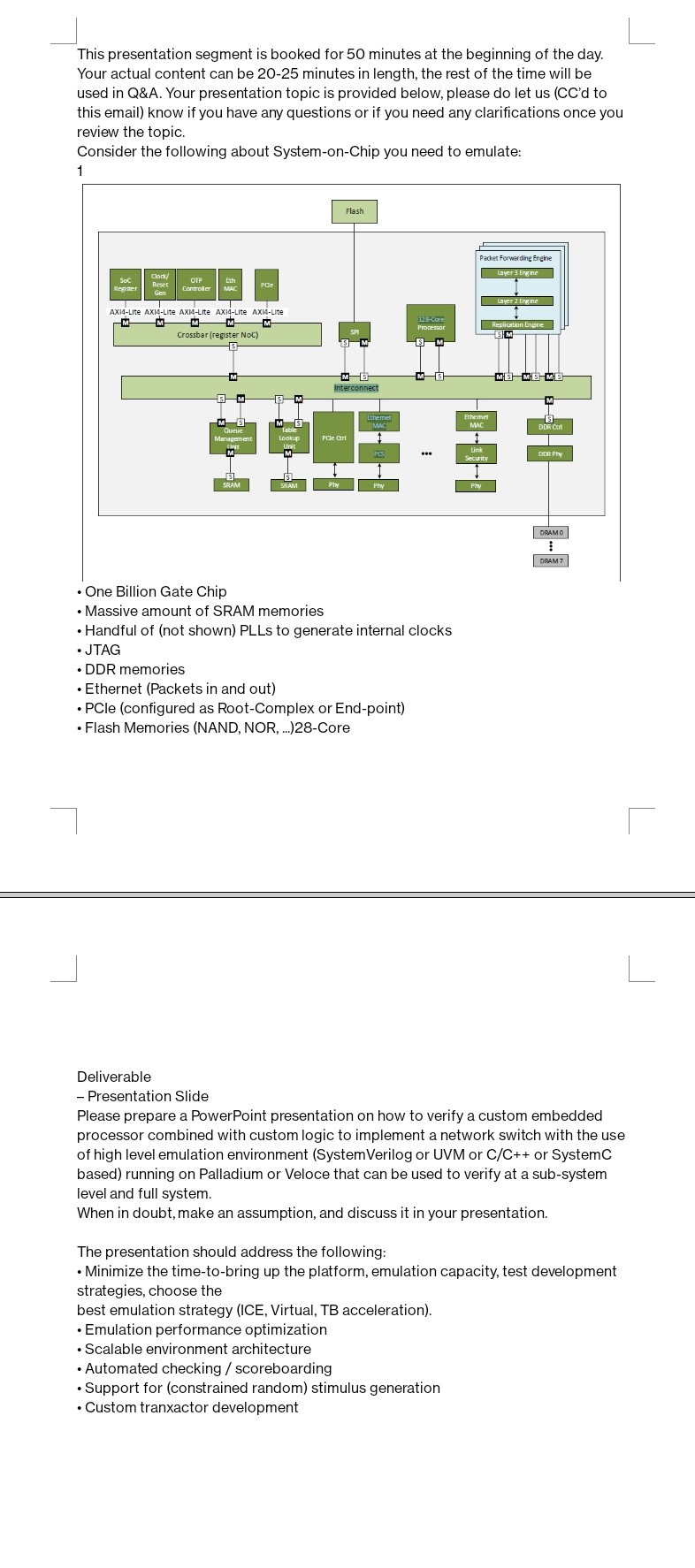

Consider the following about SystemonChip you need to emulate:

One Billion Gate Chip

Massive amount of SRAM memories

Handful of not shown PLLs to generate internal clocks

JTAG

DDR memories

Ethernet Packets in and out

PCle configured as RootComplex or Endpoint

Flash Memories NAND NOR, Core

Deliverable

Presentation Slide

Please prepare a PowerPoint presentation on how to verify a custom embedded

processor combined with custom logic to implement a network switch with the use

of high level emulation environment SystemVerilog or UVM or CC or SystemC

based running on Palladium or Veloce that can be used to verify at a subsystem

level and full system.

When in doubt, make an assumption, and discuss it in your presentation.

The presentation should address the following:

Minimize the timetobring up the platform, emulation capacity, test development

strategies, choose the

best emulation strategy ICE Virtual, TB acceleration

Emulation performance optimization

Scalable environment architecture

Automated checking scoreboarding

Support for constrained random stimulus generation

Custom tranxactor developmentis booked for minutes at the beginning of the day.

Your actual content can be minutes in length, the rest of the time will be

used in Q&A Your presentation topic is provided below, please do let us CCd to

this email know if you have any questions or if you need any clarifications once you

review the topic.

Consider the following about SystemonChip you need to emulate:

'One Billion Gate Chip

Massive amount of SRAM memories

Handful of not shown PLLs to generate internal clocks

JTAG

DDR memories

Ethernet Packets in and out

PCle configured as RootComplex or Endpoint

Flash Memories NAND NOR, Core

Deliverable

Presentation Slide

Please prepare a PowerPoint presentation on how to verify a custom embedded

processor combined with custom logic to implement a network switch with the use

of high level emulation environment SystemVerilog or UVM or CC or SystemC

based running on Palladium or Veloce that can be used to verify at a subsystem

level and full system.

When in doubt, make an assumption, and discuss it in your presentation.

The presentation should address the following:

Minimize the timetobring up the platform, emulation capacity, test development

strategies, choose the

best emulation strategy ICE Virtual, TB acceleration

Emulation performance optimization

Scalable environment architecture

Automated cscoreboarding

Support for constrained random stimulus generation

Custom tranxactor development

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock