Question: This question describes a new instruction we might consider adding to the Y86-64 processor. Like the textbook does in the section 4.3 and we did

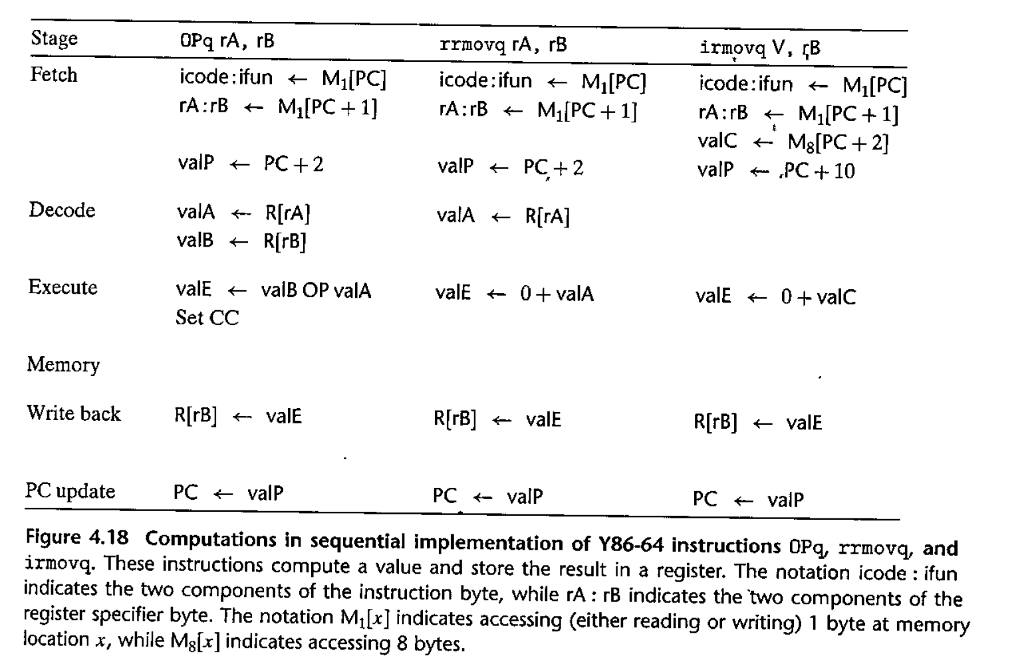

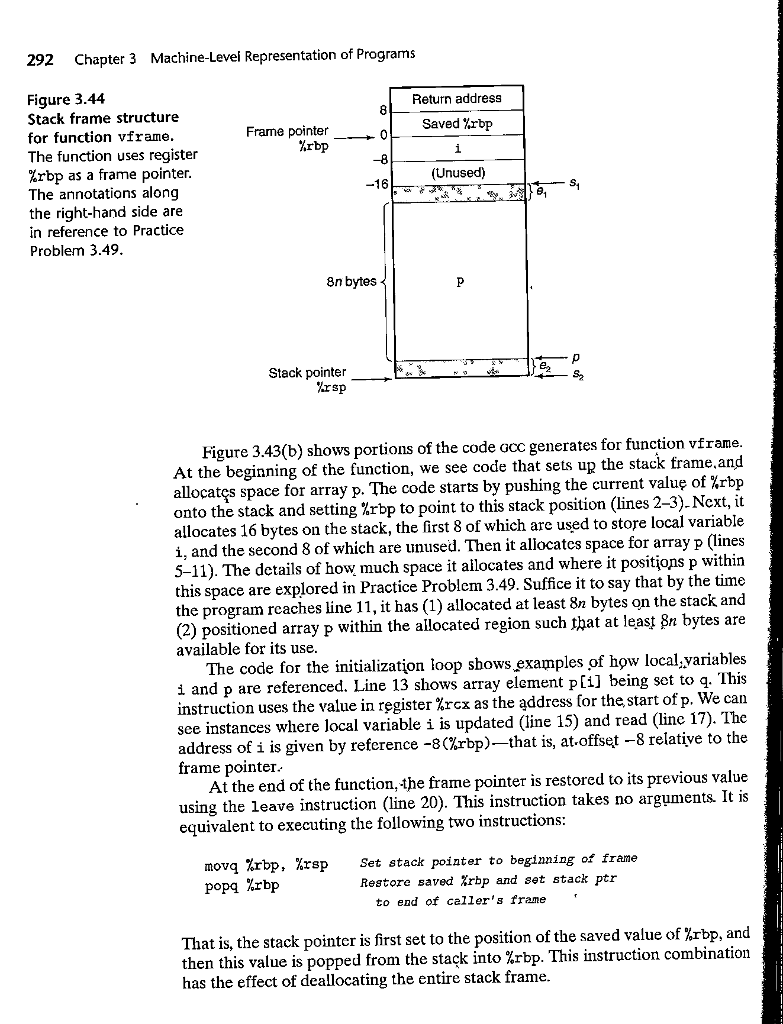

This question describes a new instruction we might consider adding to the Y86-64 processor. Like the textbook does in the section 4.3 and we did in lecture for the existing Y86-64 instructions, give the actions that a SEQ-style Y86-64 implementation would take in each stage to execute the instruction. For each instruction, you should make a table with 6 rows labeled Fetch, Decode, Execute, Memory, Writeback, and PC update (similar to Figure 4.18). Use the same notations as we did in class, with signal names like valA, and R[...] and M[... ] to represent accesses to the register file and memory. The leave instruction is used to clean up a stack frame when a frame pointer is in use (its mentioned in section 3.10.5 of the textbook, p. 292). It first copies the frame pointer %rbp into the stack pointer %rsp, and then it pops the top entry of the stack into %rbp. In other words, it is equivalent to the two-instruction sequence:

1. movq %rbp, %rsp

2. popq %rbp

|

| Leave |

| Fetch |

|

| Decode |

|

| Execute |

|

| Memory |

|

| Write Back |

|

| PC Update |

|

Figure 4.18:

P.292

rrmovq rA, rB Fetch icode : ifun M1[PC] code : ifun M,[PCI code : ifun M1[PCI valP PC +2 valP PC+2 valp ,PC + 10 Decode valA RIA] valE valBOP valA Set CC Execute Memory Write back R valE RIrB] valE RIrB] valE PC update PC valP PC valP vaiP Figure 4.18 Computations in sequential implementation of Y86-64 instructions OPq, rrmovq, and irmovq. These instructions compute a value and store the result in a register. The notation icode : ifun indicates the two components of the instruction byte, whileA:B indicates the two components of the register specifier byte. The notation Mi[] indicates accessing (either reading or writing) 1 byte at memory locationx, while Mslx] indicates accessing 8 bytes rrmovq rA, rB Fetch icode : ifun M1[PC] code : ifun M,[PCI code : ifun M1[PCI valP PC +2 valP PC+2 valp ,PC + 10 Decode valA RIA] valE valBOP valA Set CC Execute Memory Write back R valE RIrB] valE RIrB] valE PC update PC valP PC valP vaiP Figure 4.18 Computations in sequential implementation of Y86-64 instructions OPq, rrmovq, and irmovq. These instructions compute a value and store the result in a register. The notation icode : ifun indicates the two components of the instruction byte, whileA:B indicates the two components of the register specifier byte. The notation Mi[] indicates accessing (either reading or writing) 1 byte at memory locationx, while Mslx] indicates accessing 8 bytes

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts