Question: Three 3-wire DMACs (DMAC_1, DMAC_2, and DMAC_3) are connected to the 68000 processor over a bus arbiter (see lecture notes slide 6.23). The order of

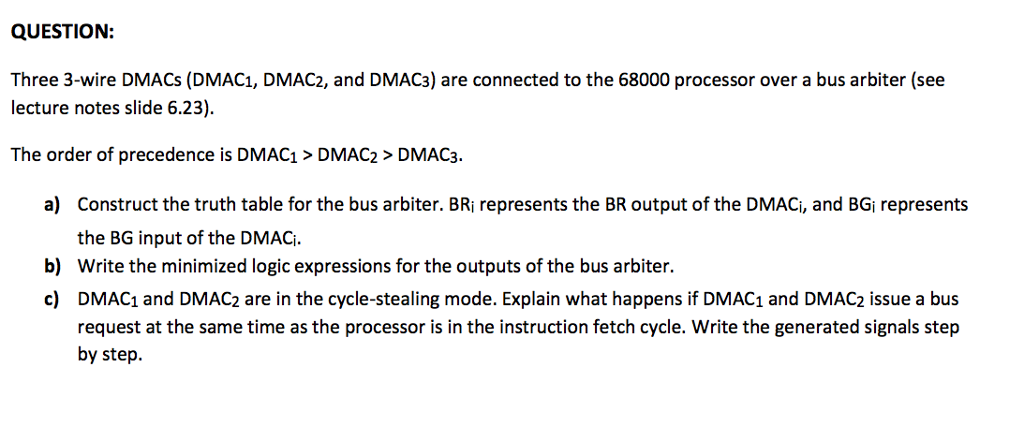

Three 3-wire DMACs (DMAC_1, DMAC_2, and DMAC_3) are connected to the 68000 processor over a bus arbiter (see lecture notes slide 6.23). The order of precedence is DMAC_1 > DMAC_2 > DMAC_3. a) Construct the truth table for the bus arbiter. BR_i represents the BR output of the DMAC_i, and BG_i represents the BG input of the DMAC_i. b) Write the minimized logic expressions for the outputs of the bus arbiter. c) DMAC_1 and DMAC_2 are in the cycle-stealing mode. Explain what happens if DMAC_1 and DMAC_2 issue a bus request at the same time as the processor is in the instruction fetch cycle. Write the generated signals step by step. Three 3-wire DMACs (DMAC_1, DMAC_2, and DMAC_3) are connected to the 68000 processor over a bus arbiter (see lecture notes slide 6.23). The order of precedence is DMAC_1 > DMAC_2 > DMAC_3. a) Construct the truth table for the bus arbiter. BR_i represents the BR output of the DMAC_i, and BG_i represents the BG input of the DMAC_i. b) Write the minimized logic expressions for the outputs of the bus arbiter. c) DMAC_1 and DMAC_2 are in the cycle-stealing mode. Explain what happens if DMAC_1 and DMAC_2 issue a bus request at the same time as the processor is in the instruction fetch cycle. Write the generated signals step by step

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts