Question: Time Delay Calculation When Timer clock source is PBCLK Case I: No prescaler 1. TT?cLiK 2. Delay = (XXXX-YYYY +1)*TTICLK Where XXXX and 1 FBCLK

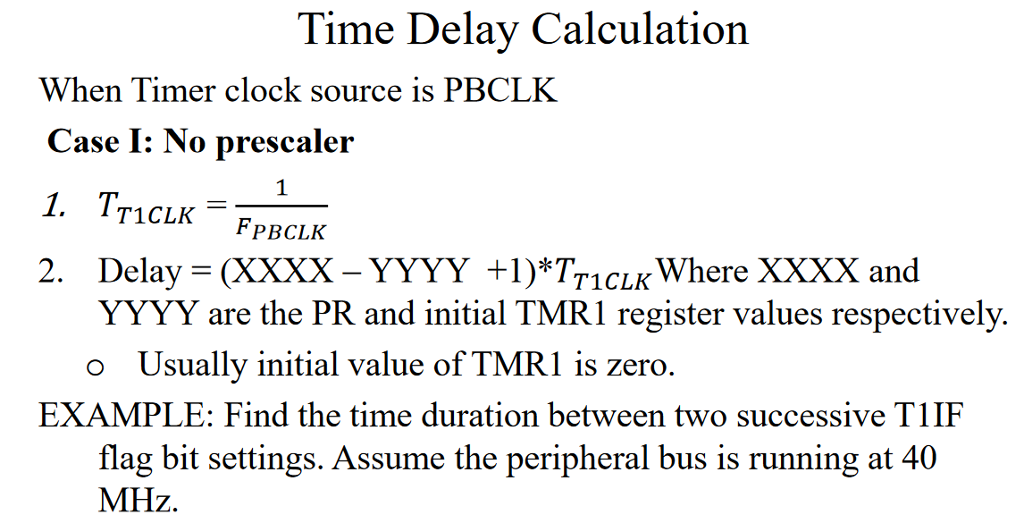

Time Delay Calculation When Timer clock source is PBCLK Case I: No prescaler 1. TT?cLiK 2. Delay = (XXXX-YYYY +1)*TTICLK Where XXXX and 1 FBCLK YYYY are the PR and initial TMR1 register values respectively. o Usually initial value of TMR1 is zero. EXAMPLE: Find the time duration between two successive T1IF flag bit settings. Assume the peripheral bus is running at 40 MHz Time Delay Calculation When Timer clock source is PBCLK Case I: No prescaler 1. TT?cLiK 2. Delay = (XXXX-YYYY +1)*TTICLK Where XXXX and 1 FBCLK YYYY are the PR and initial TMR1 register values respectively. o Usually initial value of TMR1 is zero. EXAMPLE: Find the time duration between two successive T1IF flag bit settings. Assume the peripheral bus is running at 40 MHz

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts